アルデックがHES-DVMプロトモードでFPGAのASIC設計プロトタイプ立ち上げの時間を短縮

Henderson, Nevada, U.S.A. – 2019年1月14日 – ASIC/FPGAデザイン向けHDL混合言語シミュレーションとハードウェア・アシステッド・ベリフィケーションのパイオニアであるAldec、Inc. (以下「アルデック」)は、SoCおよびASIC設計用の完全自動化およびスケーラブルなハイブリッド検証環境 HES-DVM™の最新リリースを発表しました。 リリース2018.12では、プロトタイピングモードでの自動化レベルが強化され、さらにHDLからFPGAへのコンパイルが高速化されています。

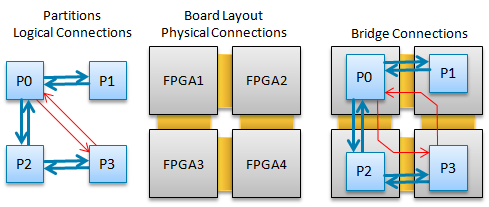

新しいHES-DVMは、FPGAプロトタイピング(FPGAを最高速度を保証するためのプリシリコンSoC検証手段として、またはハードウェアソフトウェアの協調検証プラットフォームとして使用しています)のニーズの高まりとそれに伴う課題を満たすように設計されたデザインパーティショニングおよびパーティション相互接続ツールを提供します。 仮想パーティションを使用しているため、HES-DVMは、新しいプロトタイピングボードを設計するプロセスでも使用可能でプロジェクトにとって最も効率的なボードアーキテクチャを確立できます。さらにサードパーティや自社開発のFPGAボードとの組み合わせも可能です。

2018.12リリースのHES-DVMでは、さまざまなパーティショニングシナリオを迅速に評価し、特定のプロトタイピングボードで最高のパフォーマンスを発揮するものを選択することができます。

今回のリリースでは、2つの新しい自動化機能強化が追加されたことで、FPGAプロトタイピングチームの生産性が大幅に向上しました。1つ目は自動配線で、プロトタイピングボード上に適切なチップ間トレースがない場合にフィードスルー接続を自動的に解決します。2つ目はマルチFPGAプロトタイピングボード用の自動物理接続で、これは利用可能なチップ間トレースを使用してパーティション間接続をすべてをルーティングし、インテグレートシリアル化(SERDES)や差動シグナリング(LVDS)を含むさまざまなタイプのI/Oをインテリジェントに割り当てます。

さらに、HES-DVMのエミュレーションおよびプロトタイピングモードでのデザインセットアップのターンアラウンドタイムをさらに短縮するために、Aldecは独自のHDLコンパイラを開発しました。詳細は年内に発表される予定です。

アルデックのハードウェア事業部ゼネラルマネージャー Zibi Zalewskiのコメント:

「HES-DVMの最新リリースを発表できることを誇りに思います。デザインセットアップ時間を大幅に短縮する機能を追加することで、当社のFPGAプロトタイピングおよびエミュレーションソリューションが向上し、設計者は一定時間内に以前よりも多くのプロトタイプシナリオを評価することが可能です。また、非常に短いターンアラウンドタイムで、ユーザーはバグ修正から改訂されたプロトタイプ実行の、恩恵を受けることができ、何ヶ月もの面倒な作業から解放される可能性があります。私たちはFPGAベースのエミュレーションとプロトタイピング技術の継続的な向上を目指しています。」

アベイラビリティ

新しいHES-DVM™2018.12ソフトウェアは現在入手可能です。 HES-DVMの詳細または評価については、www.aldec.comへアクセス、sales-jp@aldec.comに電子メール、+1 (702) 990-4400に電話、またはAldecの世界各地の販売代理店にお問い合わせください。

HES™ プロトタイピングについて

Aldecは、Xilinx Virtex UltraScaleおよびVirtex-7ファミリの最大サイズをベースにしたHES™ プロトタイピングボード のポートフォリオを提供しています。 これらのボードは、BPXバックプレーンと標準 FMCおよびBPX ドータカード コネクタを使用して簡単に拡張できるように設計されています。

HES-DVM™について

HES-DVM™は、SoCおよびASIC設計用の完全に自動化されたスケーラブルなハイブリッド検証環境です。SCE-MIやTLMなどの最新のコ・エミュレーション規格と最新のFPGAテクノロジを利用し、ハードウェアおよびソフトウェア設計チームはデザインのハードウェアプロトタイプへの早期アクセスを取得します。HES-DVMは、シミュレーションアクセラレーション、ハイブリッドヴァーチャルプロトタイピング、インサーキットエミュレーション、ソフトウェア検証とプロトタイピングを含むあらゆる種類のエミュレーションおよび物理プロトタイピング作業のために世界中のラボで使用されています。

アルデックについて

アルデックは米国ネバダ州ヘンダーソンに本社を置く、エレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、SoC/ASICエミュレーション・プロトタイピング、デザインルールチェック、CDC/RDC検証、IPコア、要求ライフサイクル管理、DO-254機能検証、組込みソリューション、ハイパフォーマンスコンピューティングおよび軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.