大規模HPC

従来のサーバでは消費エネルギーが大きい上に計算能力が足りなくなっている分野が数多くあります。ニューラルネットワーク、ディープラーニング、データマイニング、クラウドコンピューティング、学術研究などはそのうちのほんの一部です。近年、FPGAテクノロジが飛躍的に進化したために、HPCのアプリケーションにFPGAを応用できるようになりました。

アルデックのスケーラブルなFPGAベースのアクセラレータは大規模HPCのアプリケーションに最適です。現世代のFPGAボードは低消費電力のXilinx® Ultrascale™ FPGAを搭載し、卓越した計算能力を特徴としています。しかも省電力性はGPUベースのアクセラレータでは達成できないレベルです。

大規模HPCアクセラレータ

- HES-XCVU9P-QDR - データセンターで使用されるサーバーの内部に直接接続可能なPCIe x16を搭載したロープロファイルフォームファクタボードです。 このボードでは、FPGAと高帯域幅のQDR-II+メモリの組合わせで、アルゴリズムの高速化のために高いスループットを提供します。

- HES-XCVU9P-ZU7EV - ボードにはホストインタフェース用チップとしてXilinx Zynq UltraScale+ XCZU7と、ユーザーのアプリケーション用にXilinxUltraScale+ XCVU9Pを搭載しています。 これはDSPおよびコンピュータビジョンアプリケーションに理想的な大量のDSPブロック(6840)を含むロジックリソースになります。

- HES-US-440 - PCIe x8のケーブル接続を備えたスタンドアロンボードには、異例の容量となる550万ロジックセルを搭載した最大級のXilinx Virtex Ultrascaleデバイス、モジュール 2個で最大64GBのDDR4メモリ、高速RLDRAMが含まれています。 非常に複雑なアルゴリズムや大多数に複製されたアルゴリズムカーネルのインスタンスから恩恵を得るアルゴリズムを高速化するために使用されています。

| HES-XCVU9P-QDR | HES-XCVU9P-ZU7EV | HES-US-440 | |

|

Logic Cells |

2.5 Million | 2.5 Million | 5.5 Million |

|

DSP Blocks |

6840 | 6840 | 2880 |

|

On-chip RAM |

75.9 Mb BlockRAM 270 Mb UltraRAM |

75.9 Mb BlockRAM 270 Mb UltraRAM |

88.6 Mb BlockRAM |

|

Off-chip RAM |

432 Mb QDR-II (3x 144 Mb) Or in *-DDR version: 32 Gb DDR4 (2x 16Gb) 144 Mb QDR-II |

32GB DDR4 (2x 16GB) 2x 576Mb RLD3 |

32GB DDR4 (2x 16GB) 1152 Mb RLD3 (2x 576Mb) |

|

Host Interface |

PCI Express x16, gen3 | PCI Express x8, gen3 Zynq UltraScale+ XCZU7 |

PCI Express x8, gen2 Zynq-7000, XC7Z100 |

ホストインタフェース

PCIeを介してFPGAボードをホストワークステーションに接続することは容易ではなく、一から行った場合にはハードウェア設計の広範囲の知識が必要になります。ソフトウェア開発者は低レイヤのハードウェア統合作業をせずにすぐに使えるハードウェアプラットフォームを必要としています。このような使用モデルを理解しているアルデックは、低レイヤのPCI Express実装の詳細を隠し、開発時間を節約するHES Proto-AXIインターフェースを提供しています。AMBA AXI規格に準拠し、高速アルゴリズムカーネルをホストコンピュータのPCIeバスにブリッジするHES Proto-AXI IPコアで受信できます。

PCIeを介してFPGAボードをホストワークステーションに接続することは容易ではなく、一から行った場合にはハードウェア設計の広範囲の知識が必要になります。ソフトウェア開発者は低レイヤのハードウェア統合作業をせずにすぐに使えるハードウェアプラットフォームを必要としています。このような使用モデルを理解しているアルデックは、低レイヤのPCI Express実装の詳細を隠し、開発時間を節約するHES Proto-AXIインターフェースを提供しています。AMBA AXI規格に準拠し、高速アルゴリズムカーネルをホストコンピュータのPCIeバスにブリッジするHES Proto-AXI IPコアで受信できます。

HES Proto-AXIはホストとHESボードの間の転送に2GB/sを超える高いデータスループットを達成するように最適化されています。コンピューティングデバイスとつながるように使いやすいメモリマッピングインターフェースを提供し、ストリーミング用AXIインターフェースへの変換も簡単に行えます。DDR3、DDR4、QDR-IIなどの外部オンボードメモリの使用は、HES Proto-AXIが適切なコントローラを搭載し、AXIインターフェースからのメモリアクセスも提供しています。

迅速な統合

アルゴリズムは、Xilinx High Level Synthesis(HLS)または同様のツールを使用してCからFPGAに直接変換し、HES Proto-AXIインフラストラクチャと簡単に統合することができます。同時に提供される高水準C APIは、LinuxまたはWindows OS上で使いやすく、低レイヤのPCIeドライバを開発する必要はありません。

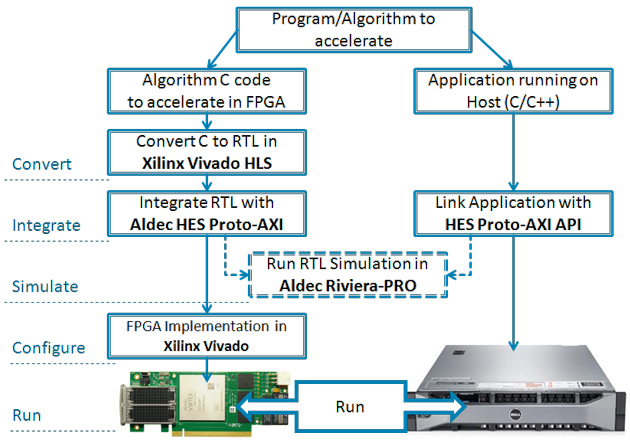

HPCデザインフローの例は、ソフトウェア言語のCからFPGAで実行するためのハードウェア記述言語のHDLに直接コンパイルするXilinx Vivado HLSツールをベースにしています。このフローは5つステージに分かれており、Aldec HPCプラットフォームのコンポーネントと完全に統合されてることがわかります。

Convert

高速化するプログラム(アルゴリズム)は2つに分割されます。1つはアクセラレータに、もう1つはホスト上で動作します。このようなパーティショニングは、Cコードのどの部分で計算負荷が高いかを示すプロファイリングをもとに行うことができます。FPGAで高速化するCコードの部分が決まったら、Xilinx Vivado HLSでCからVerilogまたはVHDLのRTLコードに変換します。このコードはさらに自動処理(合成・インプリメント)ができるようになっています。次のステージで必要となるため、RTLコードはアルデックのProto-AXIに組み込む必要があります。

Integrate

HDLコードを入手したら、AMBA AXIポートに接続されたAldec HES Proto-AXIと統合する必要があります。このステージでは、アルデックのRiviera-PROなどのHDLエディタツールで十分です。同時にホストコンピュータで実行するメインアプリケーションで、HES Proto-AXI API経由でFPGAを使用するためにアルゴリズム機能の呼び出し箇所を修正します。

Simulate

プロジェクト全体をFPGAボードで実行する前に、アルデックの高性能シミュレータRiviera-PROと大規模HPCソリューションに含まれるProto-AXIを使用し、結合/接続のミスがないか検証できます。

Configure

最後に、メインアプリケーション用のFPGAビットストリームとコンフィギュレーションファイルを生成するためにXilinx Vivado環境を使用して自動合成と配置配線を実行します。

Run

アルデックは、FPGAボードの使用を容易にするランタイム環境を提供します。PCI Expressデバイスドライバがインストールされ、アクセラレータボードのハウスキーピング機能がプログラムにリンクされたProto-AXI APIライブラリに含まれています。ホストコンピュータでメインアプリケーションを起動すると、FPGAが自動的に構成されるため、FPGAの動作やプログラミングに関する特別な知識は必要ありません。したがって、ソフトウェア開発者に最適な環境です。

主な特徴

- 複数のFPGAアクセラレータボードをプロジェクト要求に合わせて選択

- マルチボード構成によるスケーラビリティのサポート

- FPGAのホット・リコンフィギュレーションをサポート

- FPGA開発および検証環境と統合

ソリューションの内容

- HES-HPC FPGAベース・アクセラレータボード

- HES Proto-AXIホストインタフェース・モジュールとソフトウェアスタック

- RTLシミュレーション用AXIバス・ファンクショナルモデル(BFM)

- Riviera-PRO 高性能HDLシミュレータ

- リファレンスデザイン、技術文書、チュートリアル、ホワイトペーパー

- 統合サービス

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.