EfinityでActive-HDLをはじめよう

はじめに

このチュートリアルでは、EfinityでActive-HDLを使用する手順を説明します。Active-HDLはVHDL、Verilog、System Verilog、EDIF、System Cベースのデザインの開発と検証のために設計された統合環境です。このチュートリアルでは、Efinityが提供するVerilogのサンプルデザインを使用してデザイン入力とシミュレーションを行います。

事前準備

最新バージョンのEfinityソフトウェアをインストールする必要があります。

Efinity v2025.1では、パッチv2025.1.110.2.115がリリースされています。このパッチは、Active-HDLをEfinityで動作させるために必要です。

Efinixは、Efinityソフトウェアのライセンスを無料で提供しています。アカウントを作成後、ログインして、Efinity ページからライセンスを

リクエストする必要があります。その後、Efinityサポートセンターからソフトウェアとパッチをダウンロードできます。

さらにActive-HDLをインストールし、ターミナルで実行するように適切に設定する必要があります。つまりPATH環境変数にActive-HDLのパスが設定されていることを確認してください。ソフトウェアは ここから無料でダウンロードできますが、Active-HDLを使用するにはアルデックライセンスを取得する必要があります。このチュートリアルではActive-HDL 16.0を使用します。

チュートリアルを進める前に、これらの前提条件を満たしておく必要があります。

ワークスペースとデザインの作成

-

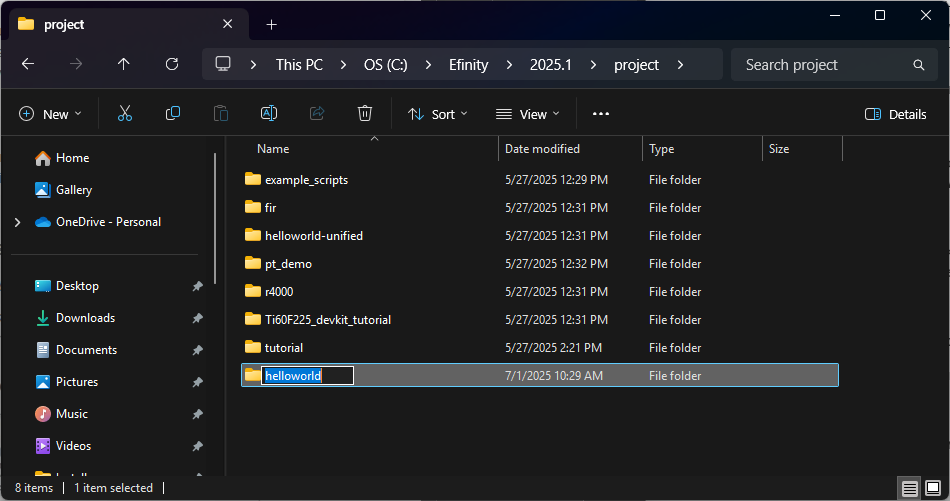

ファイルエクスプローラーを開き、/<path>/Efinity/<Efinity version>/projectディレクトリに移動し、helloworldという名前の新しいフォルダを作成します。

図 1. プロジェクトフォルダの作成

-

Efinity GUIを起動します。

-

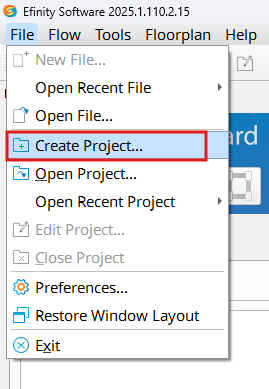

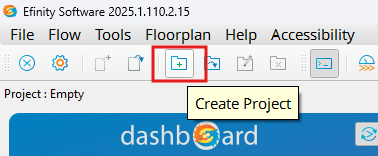

起動後、File > Create Projectを選択するか、Create Project ボタンをクリックして新しいプロジェクトを作成します。Project Editorが開き、Projectタブが表示されます。

図 2. ファイルからプロジェクトを作成

図 3. Create Projectボタン

-

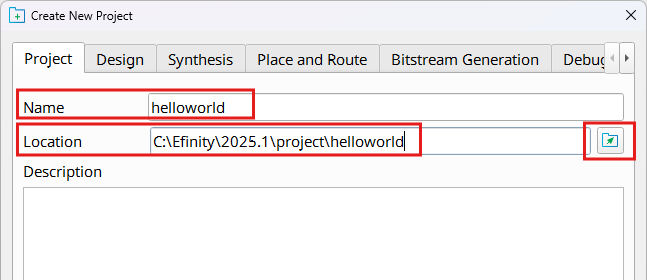

このタブで、Nameボックスにhelloworldと入力します。次にLocationボックスでボタンをクリックして、プロジェクトデータを保存するディレクトリを選択します。

/<path>/Efinity/<Efinity version>/project/helloworld

図 4. 新規プロジェクトのNameとLocationの設定

-

Descriptionボックスにプロジェクトの説明を入力します。例:My first Efinity project.

-

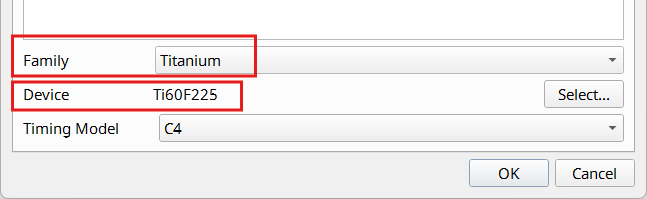

Projectタブの下部でファミリでTitanium®を選択し、デバイスとしてTi60F225を選択します。Timing Model選択はデフォルトのままにしておきます。

図 5. FPGA構成の選択

-

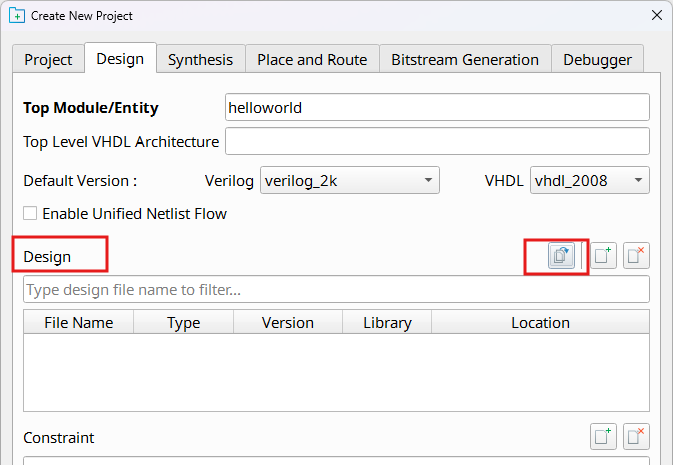

Designタブをクリックします。

-

Top Module/Entityボックスにhelloworldと入力します。

-

Designボックスの横にあるImport design and constraint filesボタンをクリックします。

図 6. "Import design and constraint files"オプションを使用したファイルの追加

ここではEfinityが提供するサンプルを使用します。

-

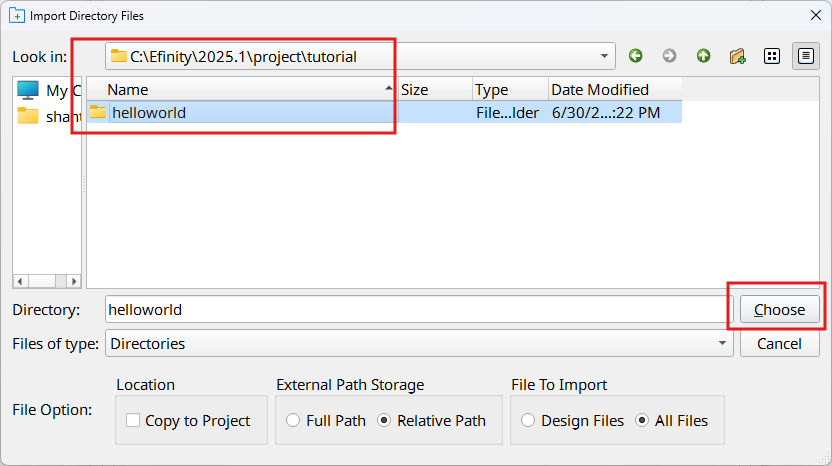

Import Directory Filesウィンドウで、

/<path>/Efinity/<Efinity version>/project/tutorial/helloworld

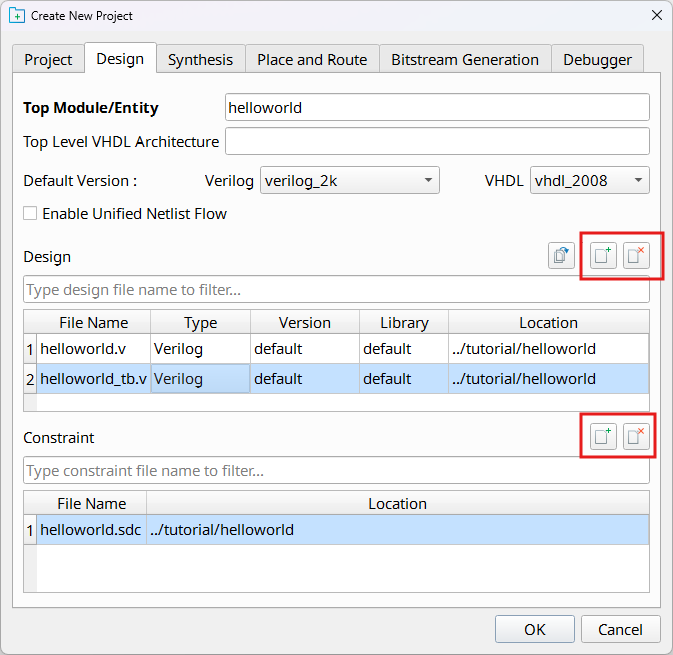

(注意:Add/Delete design/constraint fileボタンをクリックすることで、個々のデザインファイルと制約ファイルを手動で追加または削除できます。)

図 7. ファイルを追加するディレクトリの選択

図 8. ファイルを個別に追加/削除するオプション

-

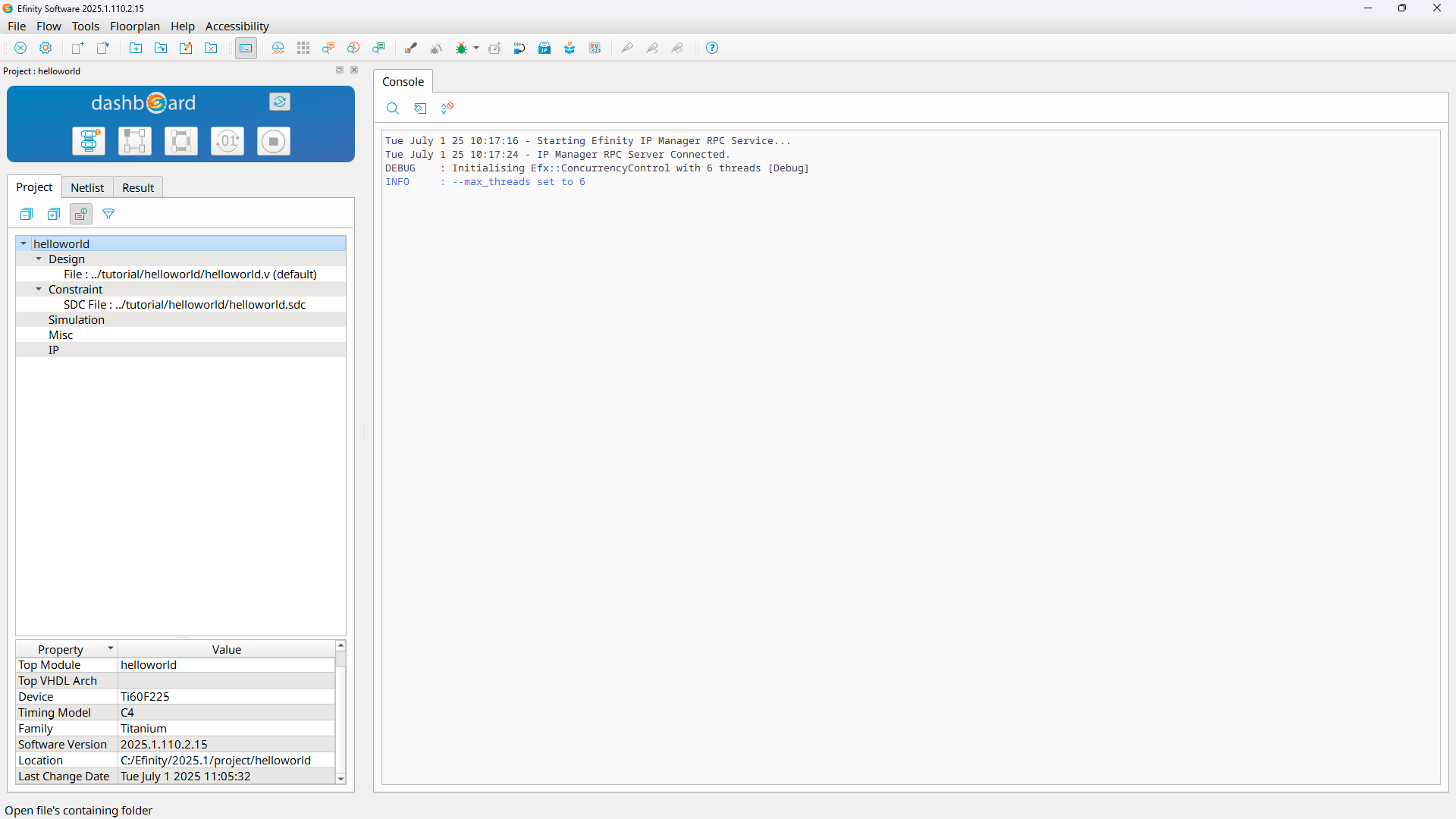

OKをクリックしてProject Editorを閉じます。Efinityプロジェクトワークスペースが作成されます。

図 9. 新しいプロジェクトワークスペース

-

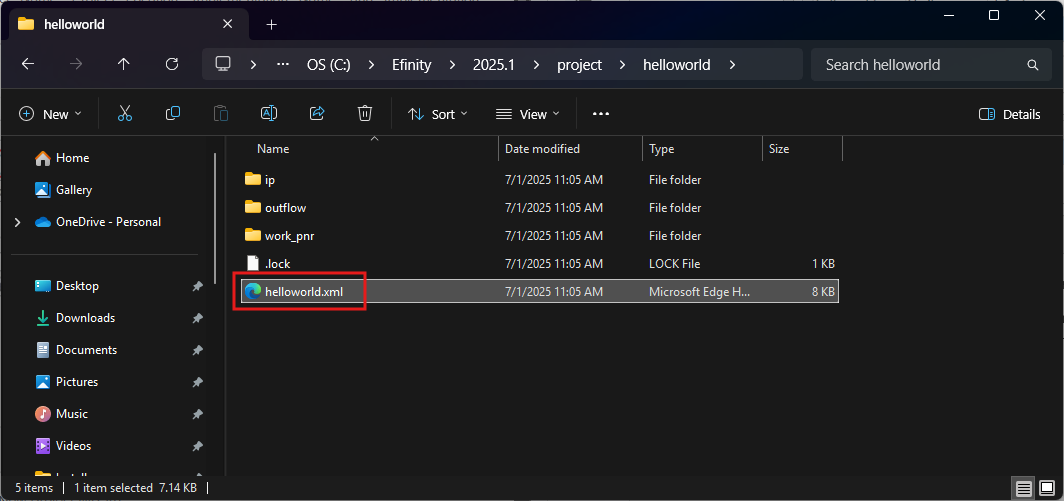

Efinityにhelloworldプロジェクトが作成されます。手順4で選択した作業ディレクトリにアクセスすると、helloworld.xmlという名前のEfinityプロジェクトファイルが作成されます。

図 10. デザインディレクトリに新しく作成されたhelloworld.xmlファイル

Designにファイルの作成/追加

-

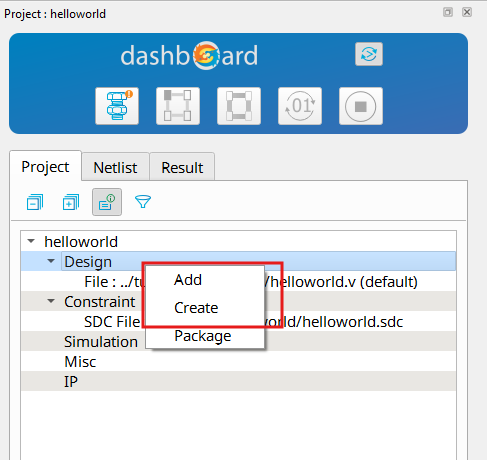

新規にファイルを作成する場合は、メインウィンドウのダッシュボードからプロジェクトのProjectタブで、目的のセクションの上で右クリック後、Createをクリックして新規プロジェクトファイルを作成します。

-

既存ファイルを追加する場合は、目的のセクションの上で右クリック後、Addをクリックして既存のファイルを追加します。

図 11. デザインセクションを右クリックしてAddおよびCreateオプションを選択

シミュレーションの実行

-

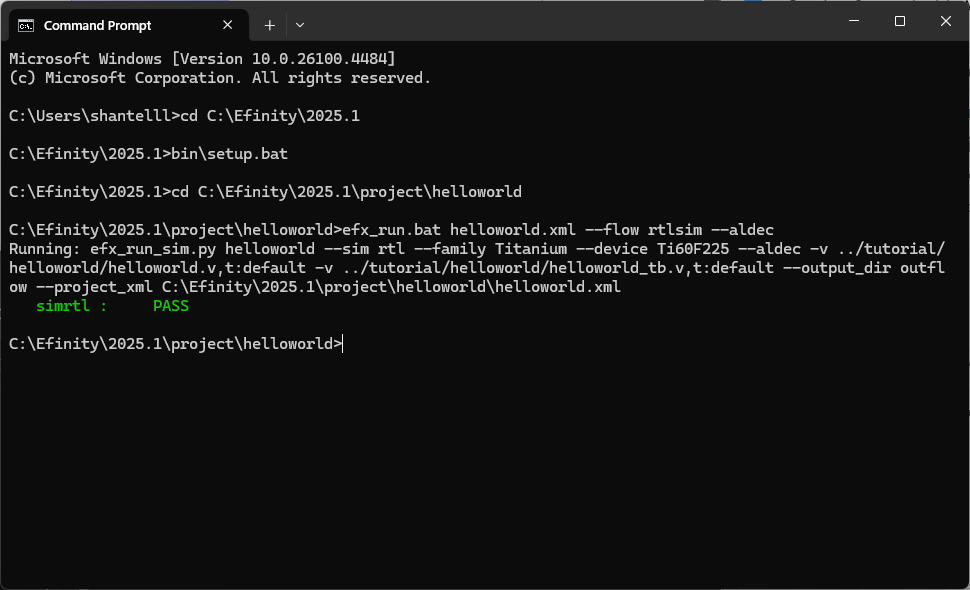

ターミナルウィンドウを開きます。

-

下記コマンドを入力します:

> cd \

\Efinity\ > bin\setup.bat > cd \ \Efinity\ \project\helloworld > efx_run.bat helloworld.xml --flow rtlsim --aldec 注意:このシミュレーションコマンドは、シミュレーションのトップレベル名が「sim」であることを前提としています。

他のデザインの場合は、末尾に引数 --tb_top <トップレベル名> を追加してテストベンチ名を定義してください。 -

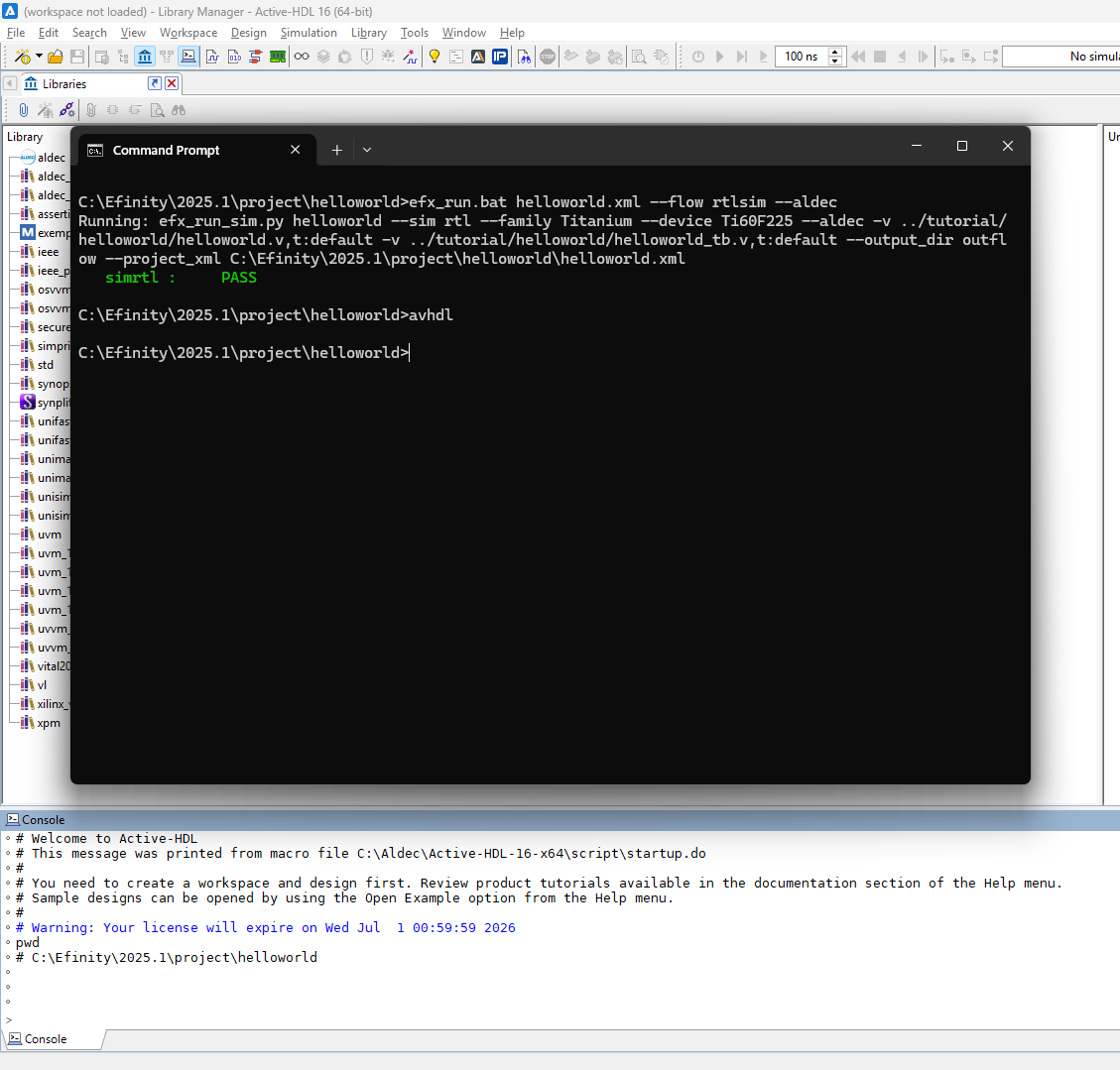

シミュレーションが正常に完了したことを示す以下のメッセージが表示されます。

Running: efx_run_sim.py helloworld --sim rtl --family Titanium --device Ti60F225 --aldec -v ../tutorial/helloworld/helloworld.v,t:default -v ../tutorial/helloworld/helloworld_tb.v,t:default --output_dir outflow -- project_xml C:\Efinity\2025.1\project\helloworld\helloworld.xml

simrtl : PASS

図 12. プロジェクトのシミュレーション実行(最終結果としてPASS)

-

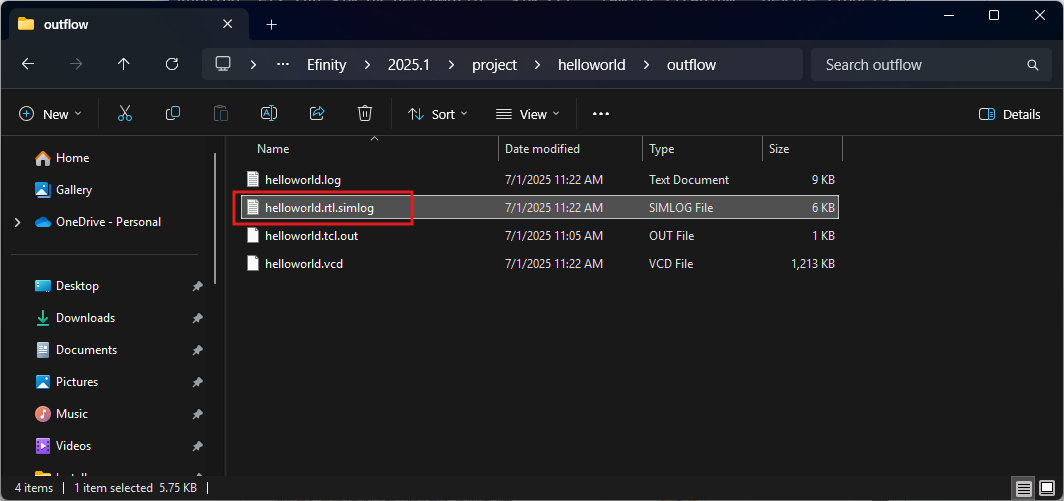

ソフトウェアはシミュレーションを実行し、結果をoutflow ディレクトリ内のhelloworld.rtl.simlogファイルに書き込みます。

図 13. helloworld.rtl.simlogの場所

-

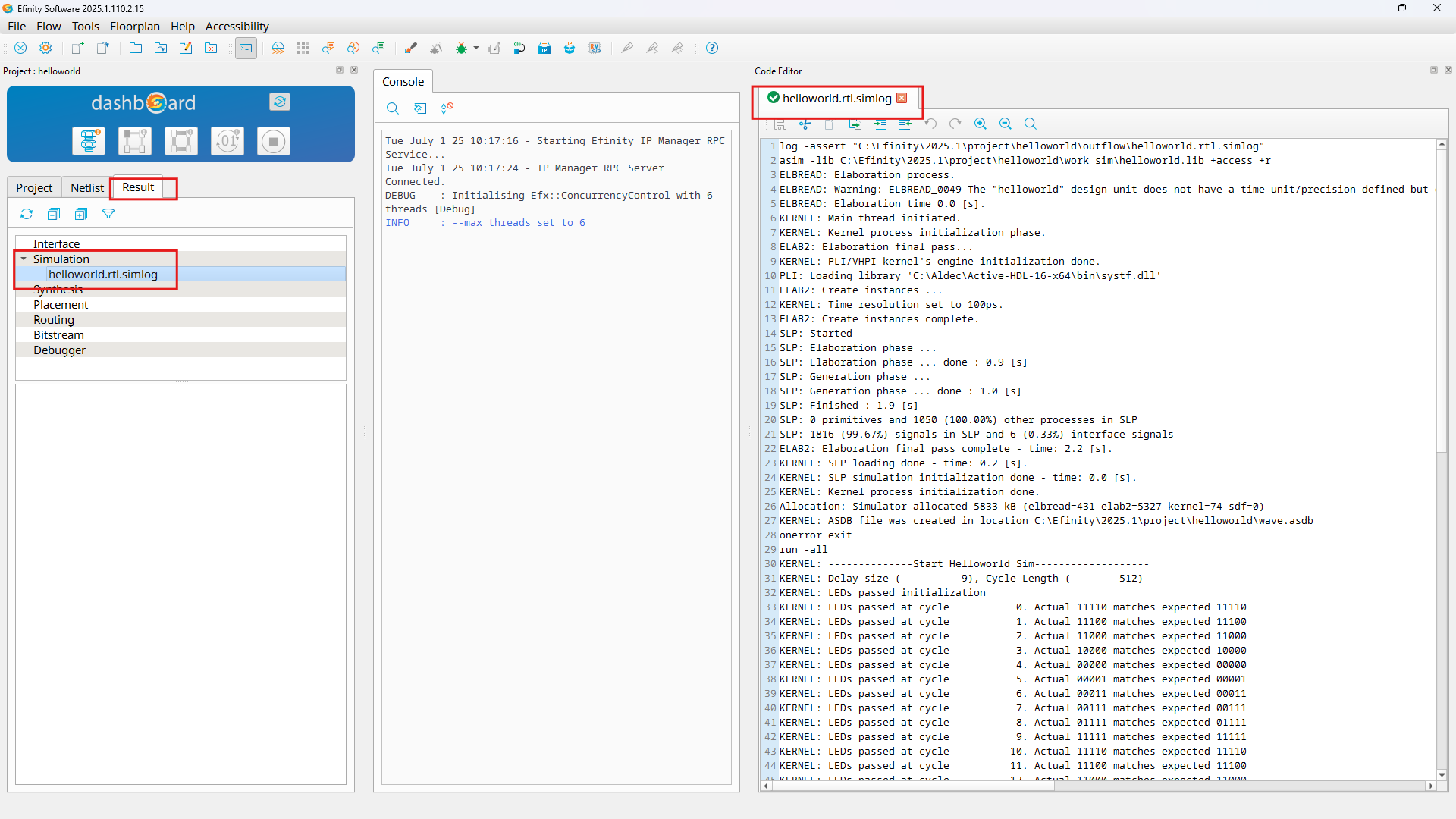

結果を表示するには、EfinityソフトウェアダッシュボードからResultタブを選択し、Simulationの三角マークをクリックして内容を展開します。次にhelloworld.rtl.simlogをダブルクリックして、Efinityコードエディターでログファイルを開きます。

図 14. Efinityプロジェクトワークスペースでのシミュレーション結果の読み込み

出力結果は以下の通りです。

KERNEL: --------------Start Helloworld Sim------------------- KERNEL: Delay size ( 9), Cycle Length ( 512) KERNEL: LEDs passed initialization KERNEL: LEDs passed at cycle 0. Actual 00001 matches expected 00001 KERNEL: LEDs passed at cycle 1. Actual 00011 matches expected 00011 KERNEL: LEDs passed at cycle 2. Actual 00111 matches expected 00111 KERNEL: LEDs passed at cycle 3. Actual 01111 matches expected 01111 KERNEL: LEDs passed at cycle 4. Actual 11111 matches expected 11111 KERNEL: LEDs passed at cycle 5. Actual 11110 matches expected 11110 KERNEL: LEDs passed at cycle 6. Actual 11100 matches expected 11100 KERNEL: LEDs passed at cycle 7. Actual 11000 matches expected 11000 KERNEL: LEDs passed at cycle 8. Actual 10000 matches expected 10000 KERNEL: LEDs passed at cycle 9. Actual 00000 matches expected 00000 KERNEL: LEDs passed at cycle 10. Actual 00001 matches expected 00001 KERNEL: LEDs passed at cycle 11. Actual 00011 matches expected 00011 KERNEL: LEDs passed at cycle 12. Actual 00111 matches expected 00111 KERNEL: LEDs passed at cycle 13. Actual 01111 matches expected 01111 KERNEL: LEDs passed at cycle 14. Actual 11111 matches expected 11111 KERNEL: LEDs passed at cycle 15. Actual 11110 matches expected 11110 KERNEL: LEDs passed at cycle 16. Actual 11100 matches expected 11100 KERNEL: LEDs passed at cycle 17. Actual 11000 matches expected 11000 KERNEL: LEDs passed at cycle 18. Actual 10000 matches expected 10000 KERNEL: LEDs passed at cycle 19. Actual 00000 matches expected 00000 KERNEL: LEDs passed at cycle 20. Actual 00001 matches expected 00001 KERNEL: LEDs passed at cycle 21. Actual 00011 matches expected 00011 KERNEL: LEDs passed at cycle 22. Actual 00111 matches expected 00111 KERNEL: LEDs passed at cycle 23. Actual 01111 matches expected 01111 KERNEL: LEDs passed at cycle 24. Actual 11111 matches expected 11111 KERNEL: Reverse direction KERNEL: LEDs passed at cycle 25. Actual 01111 matches expected 01111 KERNEL: LEDs passed at cycle 26. Actual 00111 matches expected 00111 KERNEL: LEDs passed at cycle 27. Actual 00011 matches expected 00011 KERNEL: LEDs passed at cycle 28. Actual 00001 matches expected 00001 KERNEL: LEDs passed at cycle 29. Actual 00000 matches expected 00000 KERNEL: LEDs passed at cycle 30. Actual 10000 matches expected 10000 KERNEL: LEDs passed at cycle 31. Actual 11000 matches expected 11000 KERNEL: LEDs passed at cycle 32. Actual 11100 matches expected 11100 KERNEL: LEDs passed at cycle 33. Actual 11110 matches expected 11110 KERNEL: LEDs passed at cycle 34. Actual 11111 matches expected 11111 KERNEL: LEDs passed at cycle 35. Actual 01111 matches expected 01111 KERNEL: LEDs passed at cycle 36. Actual 00111 matches expected 00111 KERNEL: LEDs passed at cycle 37. Actual 00011 matches expected 00011 KERNEL: LEDs passed at cycle 38. Actual 00001 matches expected 00001 KERNEL: LEDs passed at cycle 39. Actual 00000 matches expected 00000 KERNEL: LEDs passed at cycle 40. Actual 10000 matches expected 10000 KERNEL: LEDs passed at cycle 41. Actual 11000 matches expected 11000 KERNEL: LEDs passed at cycle 42. Actual 11100 matches expected 11100 KERNEL: LEDs passed at cycle 43. Actual 11110 matches expected 11110 KERNEL: LEDs passed at cycle 44. Actual 11111 matches expected 11111 KERNEL: LEDs passed at cycle 45. Actual 01111 matches expected 01111 KERNEL: LEDs passed at cycle 46. Actual 00111 matches expected 00111 KERNEL: LEDs passed at cycle 47. Actual 00011 matches expected 00011 KERNEL: LEDs passed at cycle 48. Actual 00001 matches expected 00001 KERNEL: LEDs passed at cycle 49. Actual 00000 matches expected 00000 KERNEL: --------------Helloworld Passed-------------------

-

設計したロジックの検証が完了しました。Efinity Interface Designerを使用してペリフェラル部分の構築を続行できます。

詳細については、Efinity ユーザーガイドをご覧ください。

シミュレーション波形の表示

Active-HDLシミュレータでシミュレーションを初期化すると.asdbファイルが自動的に生成されます。このファイルを開くと、Active-HDLの波形ビューアで記録されたシミュレーション信号を表示できます。Active-HDLは.asdbファイルに信号を記録するために、Verilogテストベンチの場合は$asdbDumpタスク、VHDLテストベンチの場合はasdbdumpプロシージャを使用できます。VHDLの場合は、テストベンチに以下のlibrary文とuse文を含める必要があります:

library aldec; use aldec.aldec_tools.all;

このチュートリアルでは、Verilog タスク $asdbDumpを使用します。

-

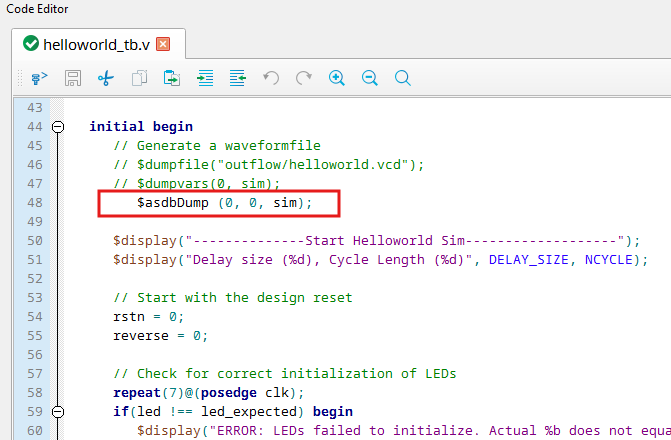

helloworld_tb.vの44行目のinitial begin文内の$dumpvars行の下に以下のコマンドを追加します:

$asdbDump (0, 0, sim);

このタスクは、トップレベル simからのすべての信号を記録します。

図 15. Efinityのコードエディタを使用してhelloworld_tb.tvに$asdbDumpを追加

-

変更を保存します。ターミナルに戻り、シミュレーションの実行セクションで示したのと同じefx_run.batコマンドを実行します。テストは再びパスするはずです。

-

現在のターミナルでavhdlコマンドを使用してActive-HDLを起動します。

図 16. ターミナルでavhdlコマンドを実行するとActive-HDL 16.0 が起動します。

-

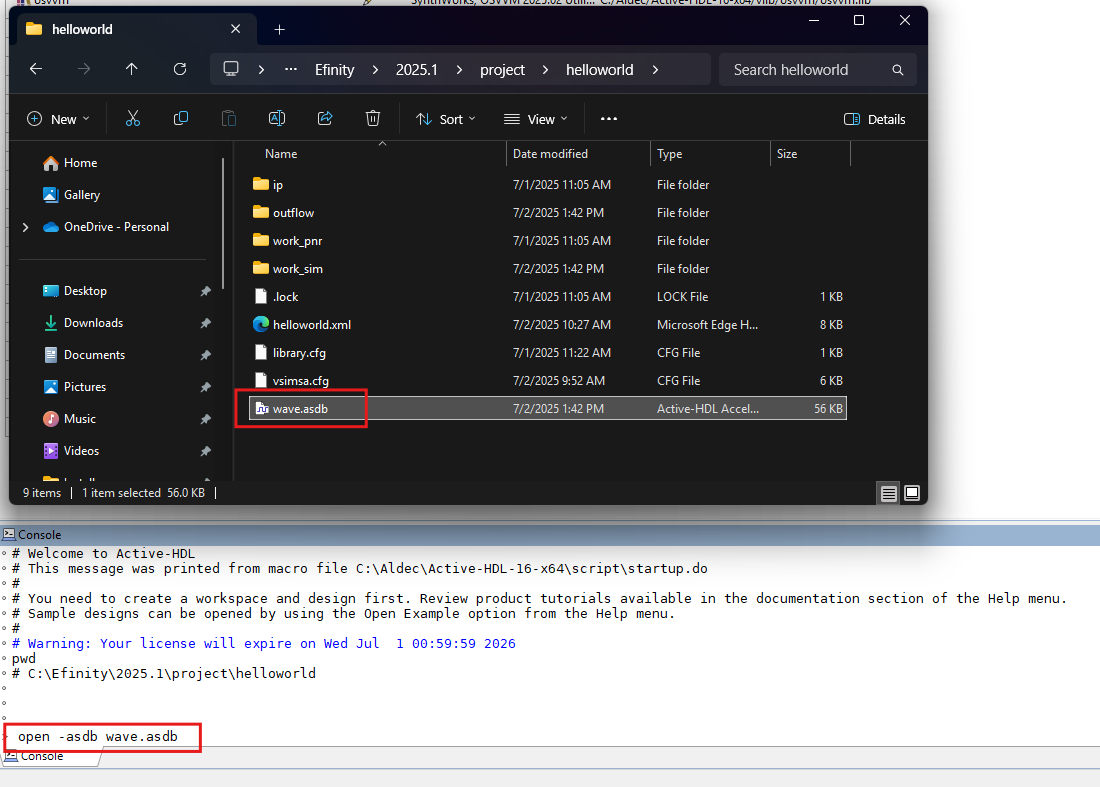

wave.asdbファイルはhelloworldフォルダ内にあります。Active-HDLのコンソールでopen -asdb wave.asdbと入力して開きます。

図 17. Active-HDLコンソールでwave.asdbの場所とopenコマンドを表示

-

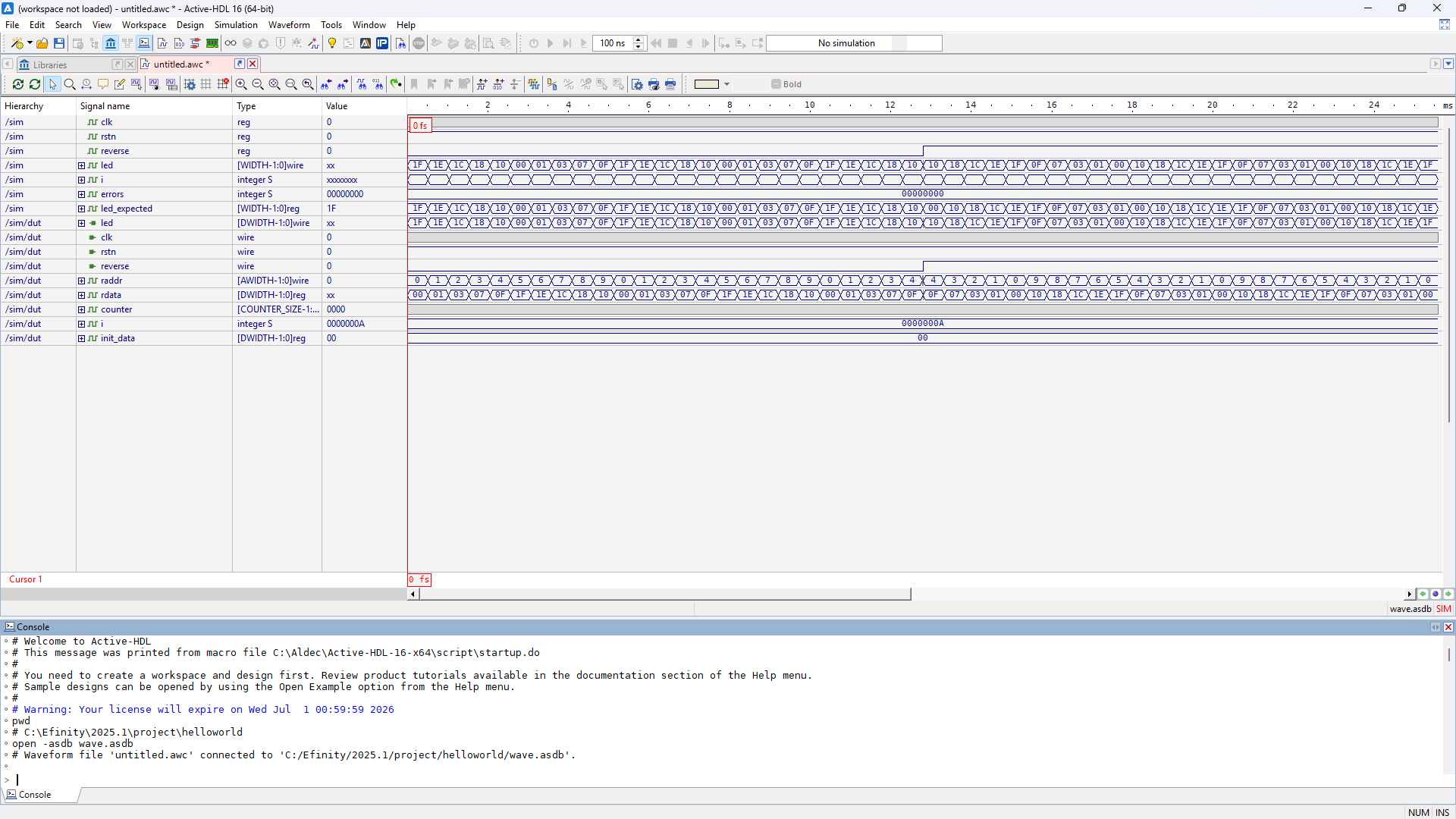

シミュレーション実行時に記録された信号とその値が波形ビューアに表示されます。

図 18. Active-HDL波形ビューアでのシミュレーション結果

-

波形ビューアには、以下のような様々なオプションが用意されています:

-

波形へのコメントの追加

-

信号を自由にグループ化

-

波形の一部をブックマーク

-

波形上の信号の色などの表示プロパティの変更

-

イベント、立ち上がり/立ち下がりエッジなどに基づいて信号履歴を参照、他...

-

波形ビューアの詳細については、こちららのビデオをご覧ください。Active-HDL GUIでは、Help > PDF/HTML Documentation > Product Helpにアクセスし、Waveform Viewerを検索してさらに詳しい情報を入手することもできます。

(注意:波形ビューアの一部のオプションは、シミュレーション後の表示では利用できない場合があります)

ヘルプ

Active-HDL に関するオンラインデータベースやその他の技術ドキュメントにアクセスするには、アルデックサポートにアクセスしてください。

サポートケースを開設したり、ソフトウェアをダウンロードしたりするには、https://www.aldec.com/supportでアルデックサポートアカウントを登録またはご利用ください。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.