SystemVerilogコンストラクトとUVMをサポートするために強化されたAldec Active-HDLの検証機能

Henderson, USA – 2019年12月3日 – HDL混在言語シミュレーションとFPGAおよびASICのハードウェア・アシステッド・ベリフィケーションのパイオニアであるAldec、Inc.(以下「アルデック」)は、FPGAデザイン設計とシミュレーション用Windowsベース統合開発環境(IDE)であるActive-HDL™の検証機能を大幅に強化しました 。

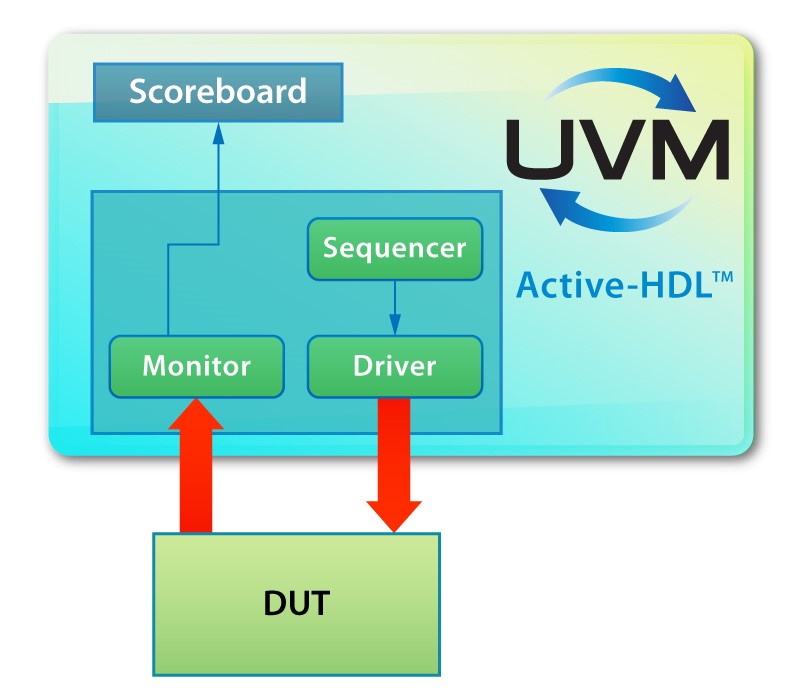

これらの拡張機能には、SystemVerilog検証コンストラクトのコンパイルおよびシミュレートする機能が含まれているため、Active-HDLはユニバーサル検証手法(UVM)テスト環境での使用、ファンクションカバレッジおよびコンストレイントランダムシミュレーションに最適です。さらに、Active-HDLのブロック図とステートマシンエディターの機能強化とともに、64ビットシミュレーション機能が選択された一般的な構成にデフォルトで追加されました。

マーケティングディレクター Louie De Lunaのコメント:

「2011年にバージョン1.0が承認されて以来、アルデックはUVMをサポートし続けています。最初にハイエンド混在HDLシミュレーター Riviera-PROでこの方法論をサポートしましたが、Active-HDL IDEがIEEE 1800.2-2017として最新のUVMライブラリもサポートするようになり、サードパーティの検証IP(VIP)を実行したいユーザーの助けになります。また、ネイティブSystemVerilog検証コンストラクトのサポートに加えて、VHDLパッケージをシミュレータでSystemVerilogパッケージとして使用できるようにコンパイルすることが可能になりました。」

Active-HDLのインストールシールドプログラムも強化され、4Kスクリーンをサポートするようになりました。さらに、ツールのGUIが一新され、メニューの変更および新しいアイコンとダイアログボックスがあります。

1997年に初めて発売されたActive-HDLは、FPGAの設計と検証のためのAldecの主力IDEです。現在、このツールのデザインフローマネージャーは、デザインの入力、シミュレーション、合成、および配置配線に200を超えるEDAおよびFPGAツールを呼び出すことができ、FPGA開発プロセス全体を通してデザインチームが単一の環境を使用することができます。Active-HDLは、 Intel®, Lattice®, Microsemi™ (Microchip™), Quicklogic®, Xilinx®などの業界をリードするFPGAデバイスをサポートしています。

Active-HDL 11.1のダウンロードと評価ができるようになりました。

Active-HDLについて

Active-HDL™は、チームベースの環境向けのWindows®ベースの統合FPGAデザイン作成およびシミュレーションソリューションです。 Active-HDLの統合デザイン環境(IDE)には、FPGAデザインの迅速な展開と検証のための完全なHDLおよびグラフィカルデザインツールスイートとRTL /ゲートレベルの混合言語シミュレータが含まれています。

アルデックについて

アルデックは米国ネバダ州ヘンダーソンに本社を置く、エレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、SoC/ASICエミュレーション・プロトタイピング、デザインルールチェック、CDC/RDC検証、IPコア、要求ライフサイクル管理、DO-254機能検証、組込みソリューション、ハイパフォーマンスコンピューティングおよび軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.