アルデック、リコンフィギュラブルFPGAベースの高頻度取引(HFT)向けアクセラレータをリリース

Henderson, Nev. – 2017年12月12日 – ASIC/FPGAデザイン向けHDL混合言語シミュレーションとハードウェア・アシステッド・ベリフィケーションのパイオニアである Aldec, Inc. (以下「アルデック」)は、極限までの低レイテンシ、高スループット、計算能力が要求される多種類の高頻度取引(HFT)戦略の実行に特化したリコンフィギュラブルFPGAベースのアクセラレータをリリースしました。

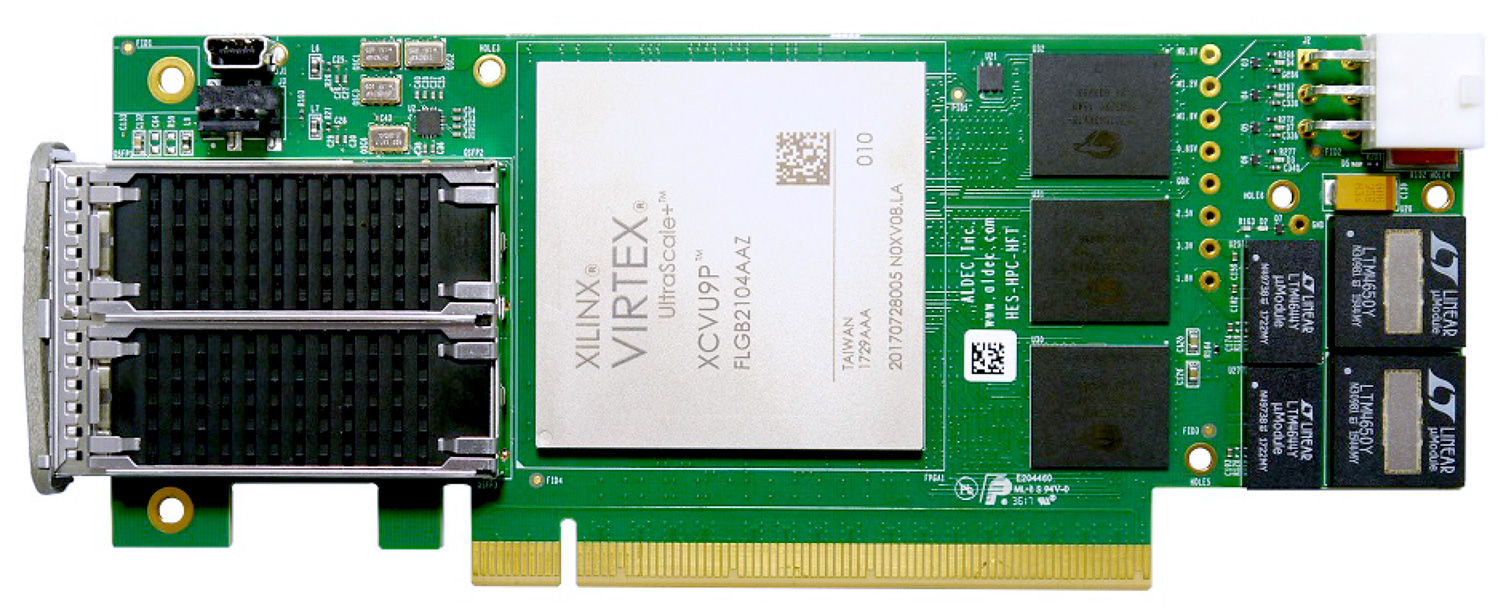

今回新たにハイパフォーマンス・コンピューティングのシリーズに加わったFPGAボードは、HFTに特化した機能が使えるソリューションです。HFTでは「低レイテンシ」が絶対に外せない条件です。これは、Xilinx の最新世代のFPGAである Virtex UltraScale+ を Ethernet、QSFP、PCI Express などの重要なインタフェースに直接接続することで実現しています。FPGAはシステム全体をシャットダウンせずにその場で再構成できます。そのおかげで設定に柔軟性が生まれ、めまぐるしく変わる取引状況に素早く反応することが可能になります。このFPGAアクセラレータは1Uラック以上の大規模取引システムと互換性があり、マーケットメイク、統計的アービトラージ、アルゴリズムトレードなどタイミングが鍵を握る取引戦略に向けたものです。

アルデックのマーケティングディレクターLouie De Lunaのコメント:

「本質的に再プログラミングが可能で、しかも大きな並列計算リソースがあるFPGAは、この5年間でHFT向けシステムに実装される例が非常に増えました。アルデックのHFTソリューションはトレード会社にとってはFPGAデザインの開発プラットフォームとなり、また1/1000秒より小さいレイテンシで取引戦略が実行できるFPGAボードでもあります。」

今回の新製品『HES-HPC-HFT-XCVU9P』はリコンフィギュラブルなFPGAをベースにしたアクセラレータで、Xilinxの Virtex UltraScale+ XCVU9P FPGA (250万ロジックセル、6,840 DSPスライス)を1個、デュアル QSFP28 の回線を有し、市場データや注文を広帯域・低レイテンシで通信します。オンボードの QDR-II+ メモリはデータ転送速度が非常に速く、高いスループットの必要な用途にも対応します。ハーフサイズ・ロープロファイルの16レーンPCIeボードは業務用ラックマウントサーバシステムで最高の性能密度を発揮します。

FPGAデザイン開発環境をお求めの方には、アルデックのFPGAアクセラレータ・ボードとRTL開発・シミュレーションツールとの組み合わせをお勧めします。例えば高性能混合言語(VHDL/Verilog/SystemVerilog/SystemC)シミュレータの Riviera-PRO はFPGA向けPythonテストベンチに対応します。また 市場データフィードハンドラなど取引システム用ブロックのインプリメントに欠かせないIPコアを提供するパートナーと協業もできます。

アルデックについて

米国ネバダ州ヘンダーソンに本社を置くアルデックは、エレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、ハードウェア・アシステッド・ベリフィケーション、SoC/ASICエミュレーション・プロトタイピング、デザインルールチェック、CDC検証、IPコア、要求ライフサイクル管理、DO-254機能検証、ハイパフォーマンスコンピューティングおよび軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.