アルデック、ARM® Fast Modelをサポートするハイブリッド・エミュレーションをリリース

Henderson, NV – 2015年10月27日 - システム設計およびASIC設計のHDL混合言語シミュレーションとハードウェア・アシステッド・ベリフィケーションのパイオニアであるAldec, Inc. (以下「アルデック」)は、ARM® Fast Modelをサポートするハイブリッド・エミュレーションをリリースします。今回発表したのは、SoCエミュレーション・ハードウェア・プラットフォームと仮想プラットフォームを簡単に連携できる新しい機能です。アルデックはFPGAとSystemCモデルを連携させることで、SoCプロジェクトの組込ソフトウェア開発の生産性を高め、市場投入時期を早めることができます。

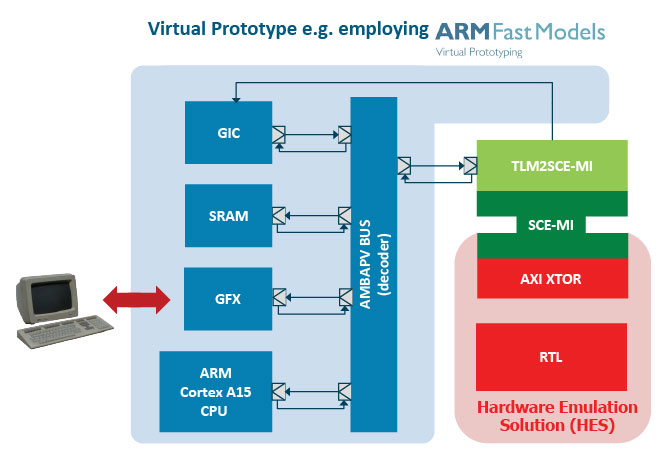

ハイブリッド・エミュレーションには中核となるコンポーネントが2つあります。それは、アルデックのHES-7™とARM®の Fast Model です。それぞれ、最先端の機能として連携し合って新しいソリューションとなります。

HES-7はアルデックのハードウェア・エミュレーション・ソリューションの第7世代としてこの名前が付いています。Xilinx®のFPGAが基盤となり、同じくアルデックのデザイン・ベリフィケーション・マネージャ(DVM)に組み込んで使います。HES-DVM™はVirtex-2000TまたはUltrascale-440を搭載するタイプがあり、1枚のボードとしては最大のFPGAリソースを搭載しています。マルチボード構成なら10億ASICゲート以上搭載可能です。

ARM Fast ModelはARMベースのSoC向けのソフトウェア開発者に、テスト・検証用ターゲット・プラットフォームをいち早く提供します。スタンドアロンの固定モデル形式か、またはARMのDS-5開発システムとの組み合わせで、ARM Fast ModelはCPUサブシステムの完全なトランザクション・レベル・モデルとなります。この仮想プラットフォームはフルスピードに近い速度で高抽象度のソフトウェアを走らせることができます。

アルデック、ハードウェア・ディビジョンのゼネラルマネージャ、Zibi Zalewskiのコメント:「ソフトウェアはSoCベース・デバイスが成功するかどうかを決める重要な要素です。開発者にとって大事なことは、できるだけ良いタイミングで最終的なシステムの上でソフトウェアをテストできることです。ARM Fast modelはソフトウェア・スタックの最上層でテスト可能で、エミュレーションではハードウェアに依存するソフトウェア・スタックの最下層で、そうしたテストが可能です。ハイブリッド・エミュレーションで、この2つの手法を結び付けて、スタック全体をカバーするアプローチが完成します。」

ソフトウェアとハードウェアの統合はSoCプロジェクトのクリティカル・パスになることが多く、ハイブリッド・エミュレーションがあるとソフトウェアチームもハードウェアチームもシリコンが完成する前、さらにはRTLやIPが完成する前にプロジェクトの最新バージョンが使えるようになります。

仮想プラットフォームとエミュレータの接続はアルデックの検証用IP(VIP)で行います。VIPはトランザクション・レベル・モデル(TLM)アダプタ、それに標準協調エミュレーション・モデル・インタフェース(SCE-MI)に準拠したバスファンクショナル・モデル(BFM)およびハードウェア・トランザクタで構成されます。VIPはUVM検証やSystemC外部テストベンチなど、他の補助的なシミュレーション環境と連携するのにも利用できます。「他社の取る非公開の独自手法ではなくSCE-MIを採用したことで、当社もお客様も、ARMなどのモデルやツールのサプライヤと連携することが簡単にできるようになりました。」とZalewskiは述べます。

アルデックはこのハイブリッド・エミュレーションを11月11日〜12日にカリフォルニア州サンタクララで開かれるARM TechConでデモします。

販売について

ハイブリッド・エミュレーションを利用するのに必要なもののうち、HES-DVM、SCE-MI、Fast ModelsはアルデックとARMから提供されています。ハイブリッド・エミュレーションについてさらに詳しいこと、または評価をご希望の方は、アルデック・ジャパン sales-jp@aldec.com までお問い合わせください。

アルデックのハードウェア・エミュレーション・ソリューション(HES)について

HES-7™はの高性能でスケーラブルなFPGAベース・汎用SoC/ASICハードウェア検証・ソフトウェア検証用プラットフォームです。HES-7は、HES-DVMと併せて、全世界の開発現場でシミュレーション・アクセラレーション、エミュレーション、ハイブリッド・バーチャル・プロトタイプ、協調エミュレーション、高速プロトタイピング、MHzスピードでのソフトウェア検証など色々な用途に使われています。アルデックのハードウェア・エミュレーション・ソリューションについて詳しくはこちらをご覧ください。

アルデックについて

1984年設立のアルデックはエレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、ハードウエア・アシステッド・ベリフィケーション、SoCおよびASICプロトタイピング、エミュレーション、デザインルールチェック、CDC検証、VIPトランザクタ、要求ライフサイクル管理、DO-254機能検証および軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。www.aldec.com

AldecはAldec, Inc.の登録商標です。その他の商標および登録商標は各所有者の財産です。

| Media Contact: | アルデック・ジャパン株式会社 宮島 健 03-5312-1791 sales-jp@aldec.com www.aldec.com |

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.