Multi-FPGA Design Partitioning

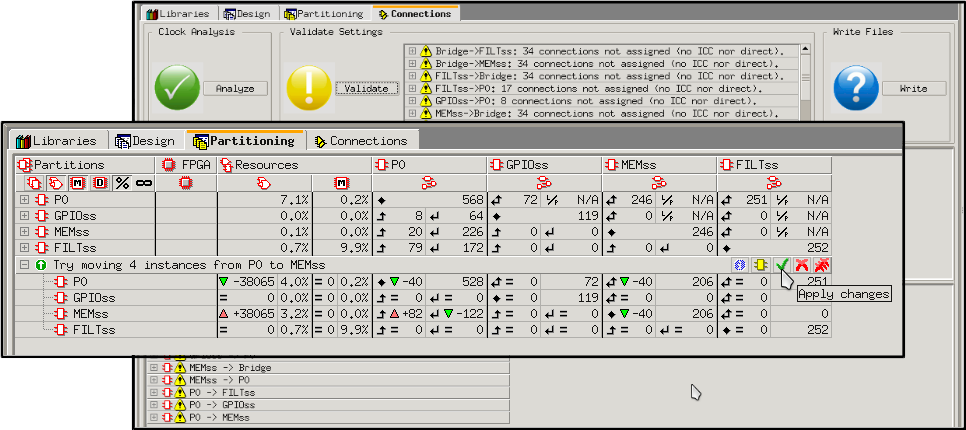

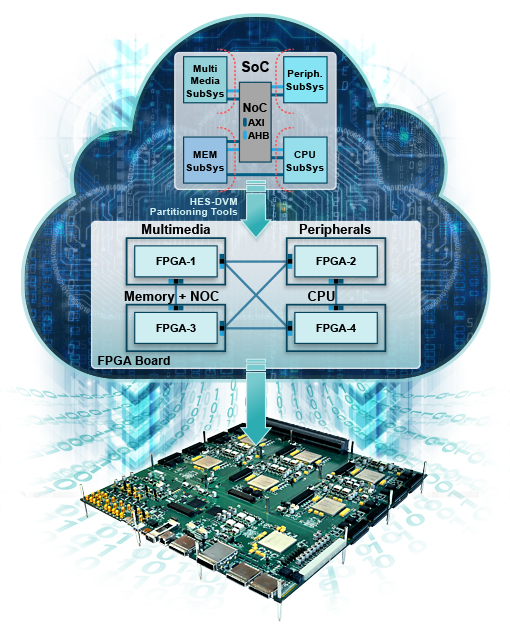

Due to the size of today’s SoC designs, the prototyping boards must contain multiple, large FPGA devices that are scalable (or expandable). Selecting the appropriate FPGA prototyping board and design partitioning solutions are among the challenges many teams are facing today. Not only the design has to be split into blocks so that each of them matches one FPGA, but also the user has to arrange interconnections between them using physical I/Os and traces available on the board. The physical interconnections of an example 633 Million ASIC gates design implemented in HES™ Prototyping Platform (with backplane) is indicated in the picture below.

The number of physical I/Os and traces is always scarce, and does not keep pace with the growing FPGA size. High speed serial I/O and LVDS transmission capable I/Os compensate for this limitation but that means the user of the FPGA prototyping platform has to implement some Time Division Multiplexing (TDM) technique in order to interconnect design partitions on the prototyping board. Another complication is proper distribution of clocks and board-level timing correctness assurance.

All these challenges are addressed with the Aldec HES-DVM software that provides prototyping flow and tools that aid in design partitioning, interconnection, clocks mapping and timing closure.

HES-DVM Proto Key Features & Benefits

- Fast-track setup for multi-FPGA prototyping

- Guided partitioning using design structure model and top-down strategy

- Instance logic replication in many partitions for clocking modules

- Monitoring utilized logic resources and interconnections

- Dry run and “what if” impact analysis to simulate many partition configurations

- Automatic conversion of gated clocks and netlist optimization

- Clock domain crossing analyzer and timing constraints editor

- Support for Aldec HES and third party custom boards

- Board-level connecting resources awareness, global clocks and traces, LVDS, single-ended

- Automatic insertion of Inter-Chip-Connection (ICC) buses

○ Use SERDES modules

○ LVDS or single-ended signalling

○ Direct routing or global traces

- Quick check-list generation for comprehensive validation of partitioning decisions

- Post-partitioning simulation support

Product Videos

HES-DVM Proto CE - Getting Started |

|

|

In this video, you learn how to use the HES-DVM partitioning tool to prepare required files for FPGA design prototyping. HES-DVM™ is a fully automated and scalable hybrid verification environment for SoC and ASIC designs. |

|

Board Compiler - Defining Custom FPGA Board for Prototype Partitioning |

|

|

In this video, Farhad Fallah from Aldec will explain how to use HES DVM board compiler tool to prepare custom board files to be used in DVM for prototyping. Board compiler is a Linux command line tool and requires the user to prepare the board file and use it as an input to the tool. |

|

Fully Automated Design Partitioning Guide |

|

|

In this video, Farhad Fallah from Aldec company provides a deep dive into automatic multi FPGA partitioning features of HES DVM tool. You'll learn how to use HES DVM on AWS cloud to partition any ASIC design into multi FPGAs automatically which takes a lot of time for the verification engineers. |

|

Deep Dive Into Design Partitioning |

|

|

Exponential increase in the number of modules in an ASIC / SoC device has become a complex challenge for verification engineers. As it's impossible to fit a big design into a single FPGA for prototyping, multi-FPGA partitioning is in high demand. |

|

Connections Tab Deep Dive |

|

|

The number of IOs used in ASIC and SoC designs are increasing almost similar to the moore's law. Because of the limitation in the number of physical IOs on FPGAs, the prototyping of more complex SoC designs that require a generous amount of IOs has become very challenging. |

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.