Active-HDL and GOWIN Flow

Overview

GOWIN provides unencrypted, flattened post-synthesis verilog files for IP simulation.

Preparing GOWIN Example

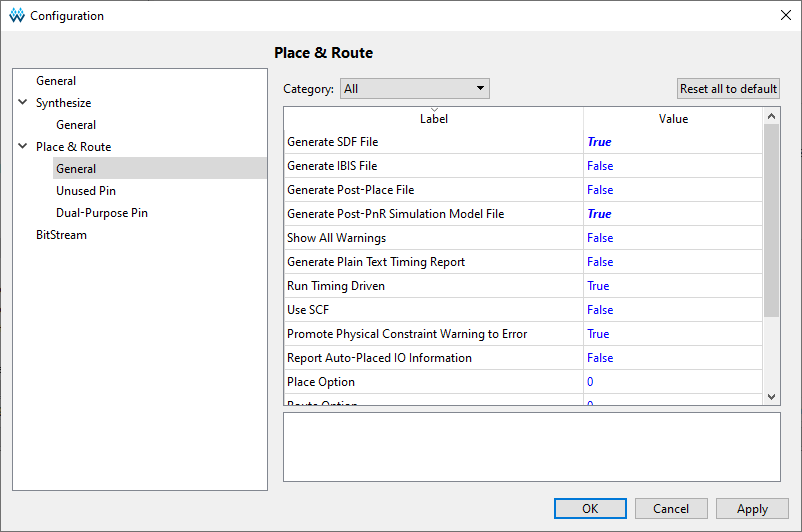

Create a project on GOWIN IDE and then change the following settings in Project->Configuration

Figure 1: GOWIN project configuration

Then, create an Active-HDL project in the same folder as GOWIN.

createdesign -nodesdir fpga_project_03 F:\temp\fpga_project_03

Preparing Libraries

GOWIN currently offers two families: gow1n and gow2a. To compile appropriate primitives, use the following compilation script:

alib gow1n_sim alog -work gow1n_sim $GOWIN_PATH\IDE\gow1n\prim_sim.v alib gow1n_tsim alog -work gow1n_tsim $GOWIN_PATH\IDE\gow1n\prim_tsim.v alib gow2a_sim alog -work gow2a_sim $GOWIN_PATH\IDE\gow2a\prim_sim.v alib gow2a_tsim alog -work gow2a_tsim $GOWIN_PATH\IDE\gow2a\prim_tsim.v

Importing IP

Follow the next steps:

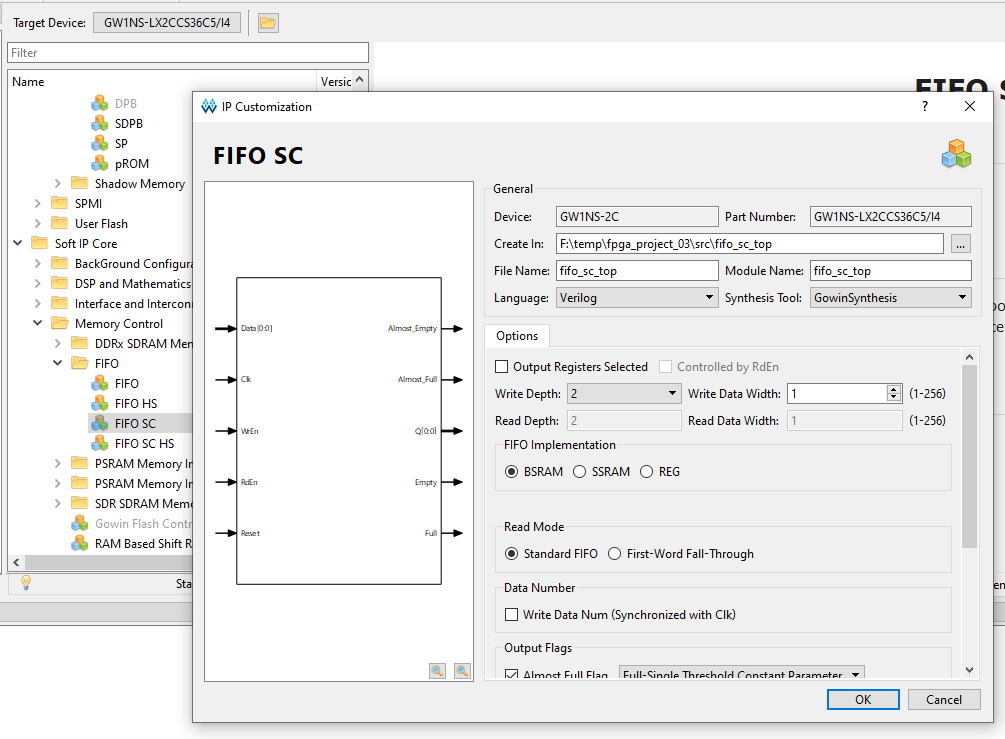

Generate an appropriate IP from the IP Core Generator by going to Tools-> IP Core Generator. Double click on FIFO SC as shown in Figure 2.

Figure 2: GOWIN IP Core Generator

Open the generated Verilog IP in Active-HDL.

Remove the protected section from `pragma protect begin_protected to `pragma protect end_protected

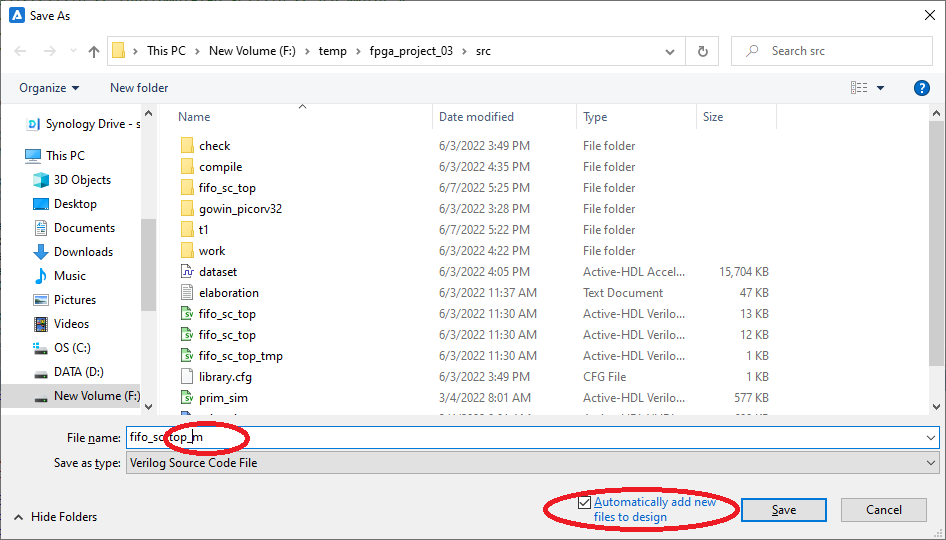

Save the file with another name and attach it to the Active-HDL design as shown in figure 3.

Figure 3: Active-HDL "Save As" window

Compile the modified file. As a result, the module entry will be compiled and added to the Active-HDL project.

Designing with Active-HDL

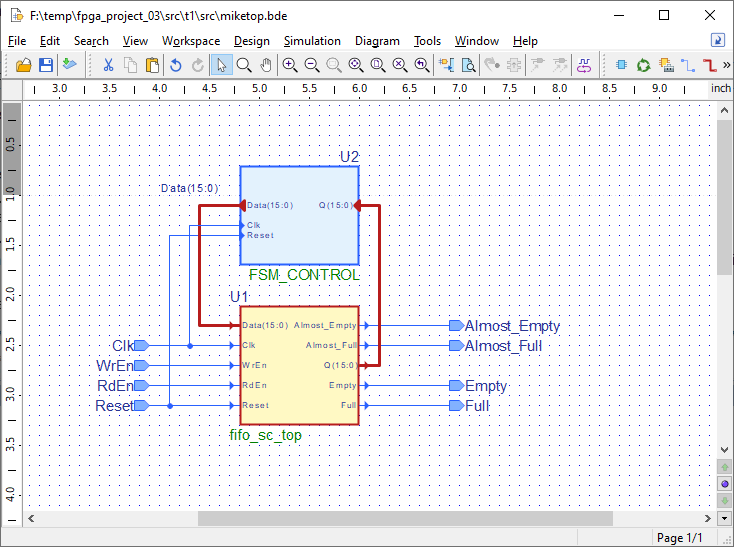

Now you can use the imported IP to create more complex levels using Block Diagram, FSM or HDE Editor.

Figure 4: Active-HDL Design includes GOWIN IP

Once the project is ready, import all of the new sources back into the GOWIN project and then run the synthesis.

Simulating with Active-HDL

Import the netlist and SDF from the GOWIN project into Active-HDL.

Compile it and use the previously created libraries, gow1n_sim or gow1n_tsim, for timing back notation.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.