HESを使用したVivadoデザインのシミュレーションの高速化

目次

はじめに

FPGAデザインがムーアの法則と同じくらい急速に成長するにつれ、検証はより大きな課題になり、HDLシミュレーションは急速に大きなボトルネックになりつつあります。 このアプリケーションノートでは、アルデックのHES-DVMを使用してシミュレーションを高速化し、シミュレーションのボトルネックを修正する方法を示します。

複雑なFPGAデザイン検証の課題

FPGAデバイスのサイズが急速に大きくなるのに合わせて、FPGAの設計/検証のエコシステムも急速に変化しています。最大のXilinx Virtex UltraSCALEチップは、440万個のロジックセルを備えており、別の指標を用いれば5,000万個相当のゲートカウントとなります。

Virtex-7以降のFPGAの効率的な設計プロセスを可能にするために、XilinxはVivado Design Suite(略してVivado)と呼ばれるソフトウェアを提供しています。従来のHDLデザインフローをサポートするだけでなく、IPインテグレーター、システムジェネレーター、さらには高位合成などの便利なシステムレベルのデザインツールも提供します。これらは、大規模で複雑なデザインの設計で非常に便利です。ライブラリからのIPコア、またはアルゴリズムの記述から自動的に生成されたIPコアを使用すると、複雑なシステムを数か月ではなく1週間で構築できます。また、XilinxがIPを相互接続するためのAXI標準を導入することを決定したことにも注意してください。これにより、再利用性が向上し、設計プロセスがさらに加速されます。言うまでもなく、Vivadoは構成可能なAXIインターコネクトIPを提供し、階層型ネットワークオンチップ(NoC)の迅速な設計と評価を可能にします。

検証は常にプロジェクトのスケジュールの中で大きな割合を占めており、HDL シミュレーションはそのプロセスの主要な段階でした。それは今も変わりません。XilinxはネイティブHDLシミュレータをVivadoにバンドルすることも決定しました。最小のFPGAデバイスのデザインをシミュレートするには十分ですが、大きなデバイスの場合はボトルネックになります。これがVivadoがアルデックのRiviera-PROなどの別のEDAベンダからサードパーティのシミュレータを選択できる理由の1つだと思います。

このような大規模デザインでは、最速のサードパーティシミュレータでさえ、それほど長くないテストシナリオのシミュレーションに何時間も費やします。このような場合、多くのエンジニアはシミュレーションをスキップして、FPGAプロトタイピングにすぐに飛び込もうとします。フロントエンドとバックエンドの両方のデザインフローがVivadoによって便利に統合されているため、合成の起動とジョブの配置とルーティングが非常に簡単で、2時間以内に最初のFPGAビットファイルを取得できます。しかしFPGA をボードにプログラミングした後に期待通りの動作をしないと、すぐに厳しい現実に直面することになります。たとえXilinx ChipScopeを接続するだけの知識があったとしても、選択したデバッグプローブが適切でないことがすぐにわかります。HDLシミュレーションに戻る時が来たのです。

もし同じような経験があるなら、HDLシミュレーション・アクセラレーションを検討すべきです。アルデックは長年にわたり、Xilinx FPGAをベースにしたエミュレーションソリューションを提供しており、ASICデザインで成功を収めてきました。しかし、最近ではFPGAデザインのサイズが急速に拡大しているため、シミュレーション環境のアップグレードが必要になっています。このアプリケーションノートでは、Vivado Design Suite で作成されたデザインのシミュレーションアクセラレーションについて説明します。

Vivadoのサンプルデザイン

シミュレーションアクセラレーションを使用するメリットは、大規模デザインのごく一部であっても確認することができます。例えばメモリサブシステムは様々な方法で構成できますが、どのデザインにも当然存在します。このサブシステムは、FPGA内の複数のサブシステムに対して、オフチップのDDR3 SDRAMメモリモジュールへのアクセスを提供します。

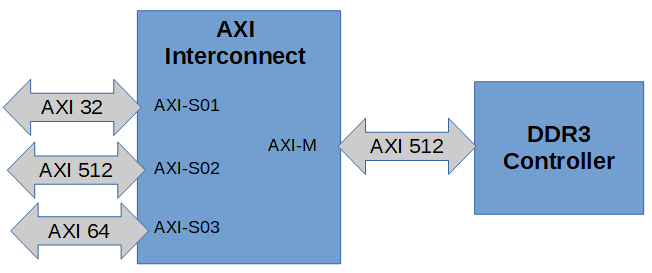

図1に示すようにDDR3コントローラとAXIインターコネクトが、このようなメモリサブシステムの主要なブロックとなります。

-

DDR3 SDRAMコントローラ

-

AXIインターコネクト

図 1. DDR3メモリサブシステム

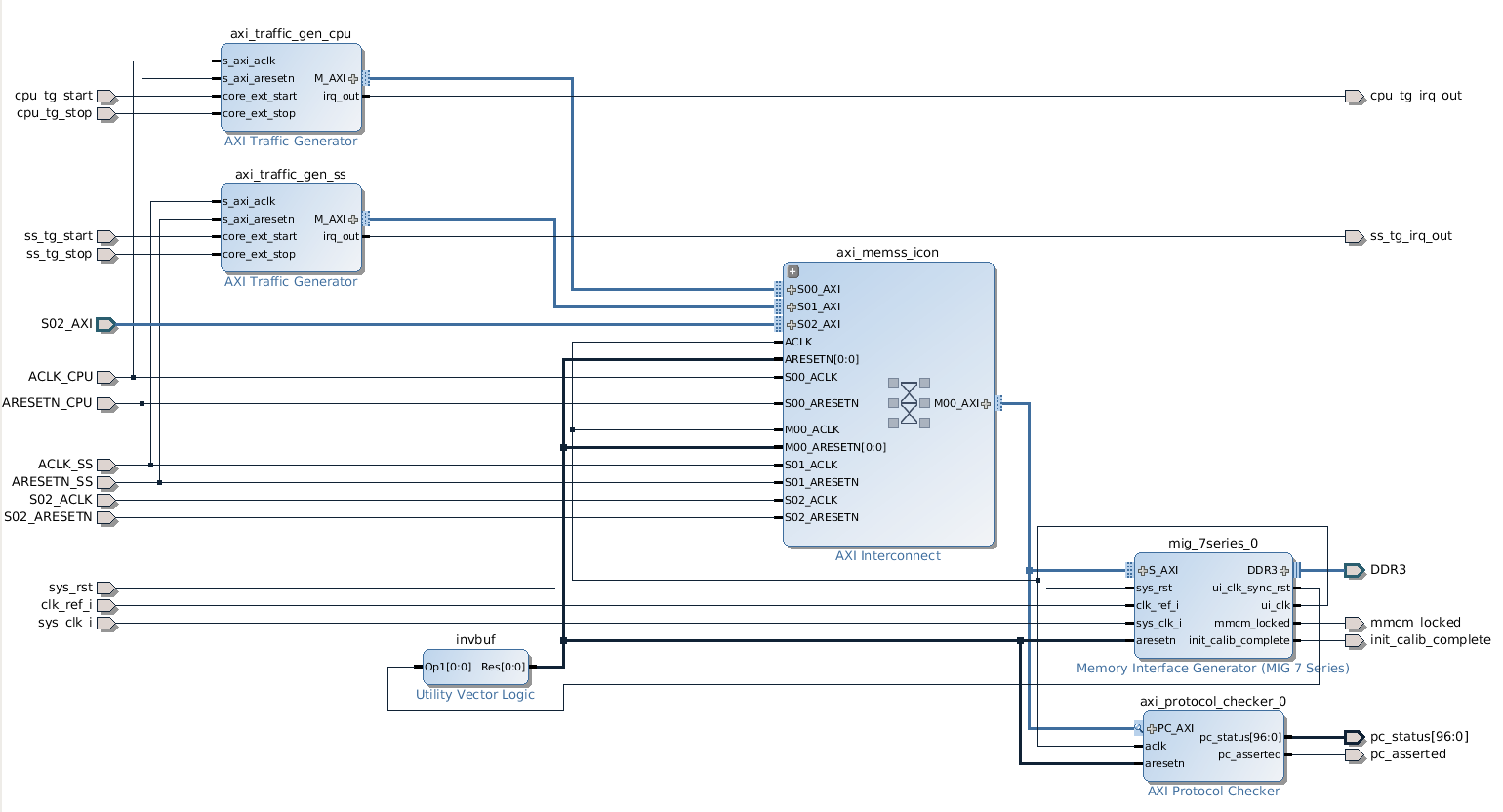

図2に示すように、VivadoIPインテグレーターとダイアグラムエディターを使用してビルドできます[1]。

図 2. VivadoデザインエディタのDDR3メモリサブシステム

このブロック図の2つの主要なIPブロックは次のとおりです:

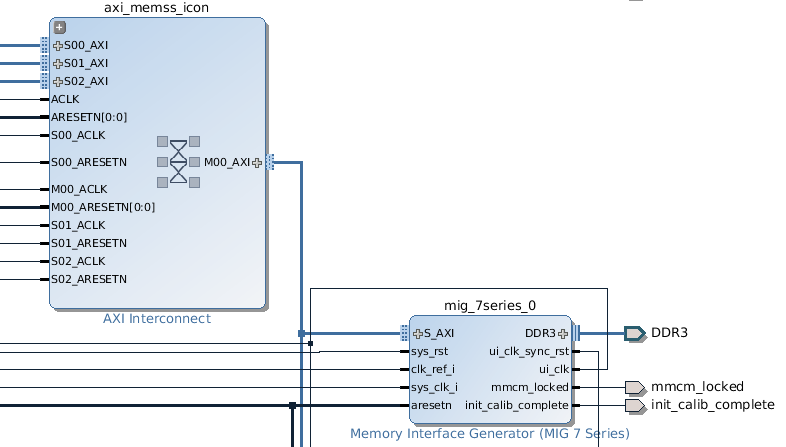

1. メモリインターフェイスジェネレーター(MIG) - アプリケーションインターフェイスとしてDDR3コントローラーとAXIスレーブを提供します。

2. AXIインターコネクト - 異なるデータサイズの3つの独立したAXI4スレーブポートを提供し、共有DDR3メモリへのアクセスを調停します。

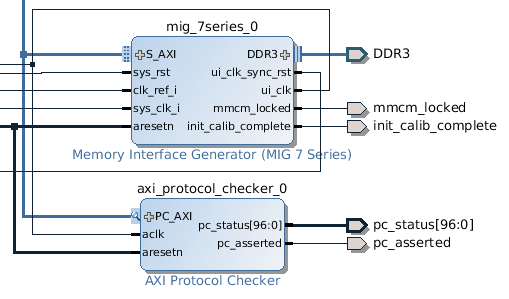

図 3. AXIインターコネクトとMIGブロック

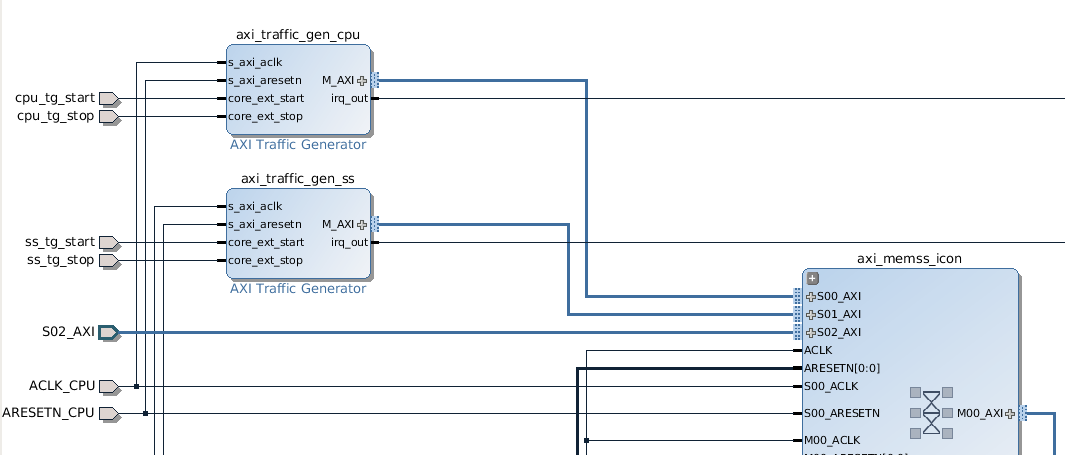

検証のために、いくつかのブロックを追加しました:

3. AXIトラフィックジェネレータ - 他のサブシステムを代表して、AXIインターコネクトの3つのスレーブポートのうち2つにAXI転送を注入します。

図 4. トラフィックジェネレータ

4. AXIプロトコルチェッカ - AXIインターコネクトとMIGコントローラ間のAXIバスを監視します。 プロトコルチェッカは、AXIバスのステータス情報を提供します。

図 5. AXIプロトコルチェッカ

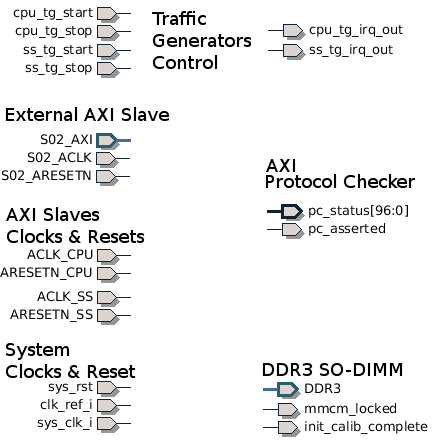

なお、上記のブロック(1~4)はすべて合成可能です。インターコネクトの描画には、Vivado Diagram Editorツールを使用します。インスタンス化されたIPの一部のポートは外部になります。その内容は次のとおりです:

図 6. 外部IOポート

サンプルデザインのシミュレーション

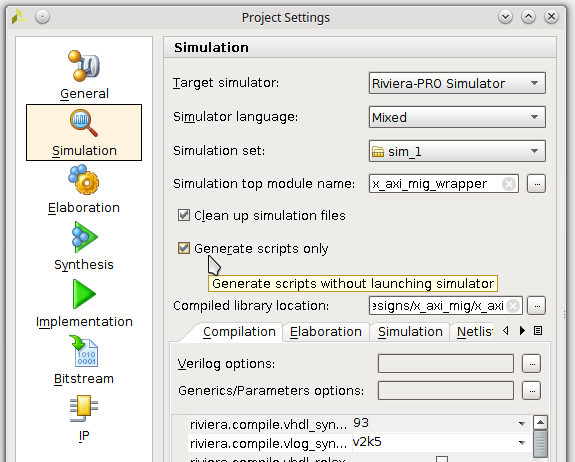

図2に示すデザインは、Vivado Project Settingsダイアログボックスで選択可能なアルデックのRiviera-PROシミュレータを使用してシミュレーションできます。 Riviera-PROはスタンドアロンで使用するため、"Generate scripts only"オプションを設定します。

図 7. Vivado Project SettingsでのデフォルトシミュレータとしてRiviera-PROを設定

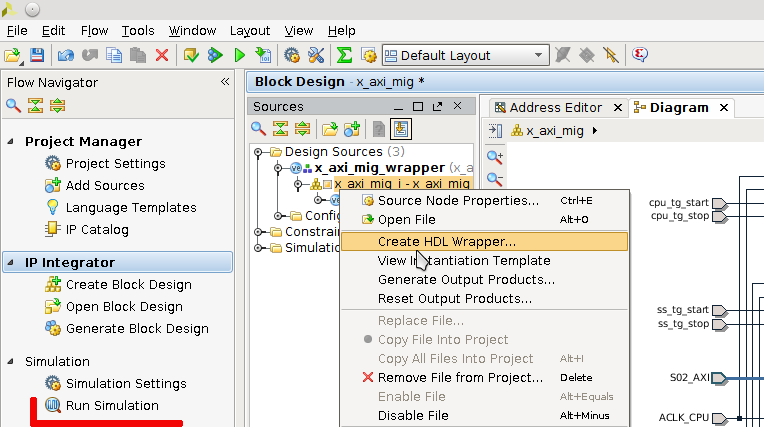

次に"Create HDL Wrapper..."オプションを使用してHDLソースコードを生成し、Flow Navigator(図8)で"Run Simulation"を呼び出して、必要なすべてのスクリプトを含むシミュレーションフォルダーを作成する必要があります。

図 8. Vivadoからシミュレーションを起動

Vivadoで生成されたシミュレーション スクリプトを使用して、ダイアグラムの HDL ラッパおよびダイアグラムで使用されているすべてのIPブロックをコンパイルすることができます。ただし、スティミュラスの生成に使用できるテストベンチはありません。これは別途開発する必要があります。

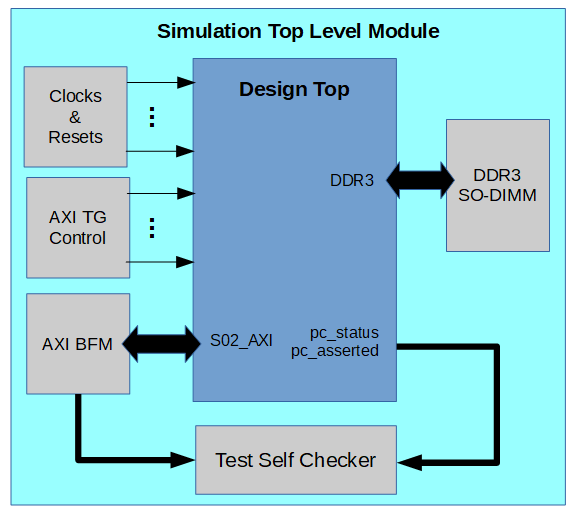

シミュレーションのテストベンチ

テストベンチではクロックやリセットなどのすべての入力をドライブし、外部に設けたAXIスレーブポートの1つ(S02_AXI)にトラフィックを発生させます。また、デザイントップとDDR3メモリのシミュレーションモデルとの接続も行います。このデザインには、2つの組み込みAXIトラフィックジェネレータがあり、それらのスタート/ストップ/IRQポートもテストベンチで制御する必要があります。最後にテストベンチは、AXIプロトコルチェッカの出力(pc_status、pc_asserted)を監視し、セルフチェック機能を備えていなければなりません。図9にこのようなテストベンチのブロック図を示します。

注意: Vivadoでは一部のIPに対してサンプルプロジェクトを提供しています。これらのプロジェクトには、必要なシミュレーションモデルと

テストベンチが含まれています。このデザインでは、MIG IPのDDR3シミュレーションモデルおよびシミュレーションラッパを再利用しています。

図 9. テストんベンチのブロックダイアグラム

テストベンチの準備ができたら、シミュレーションを実行し、さらにシミュレーションの加速に移行して、スピードアップがあるかどうかを確認します。

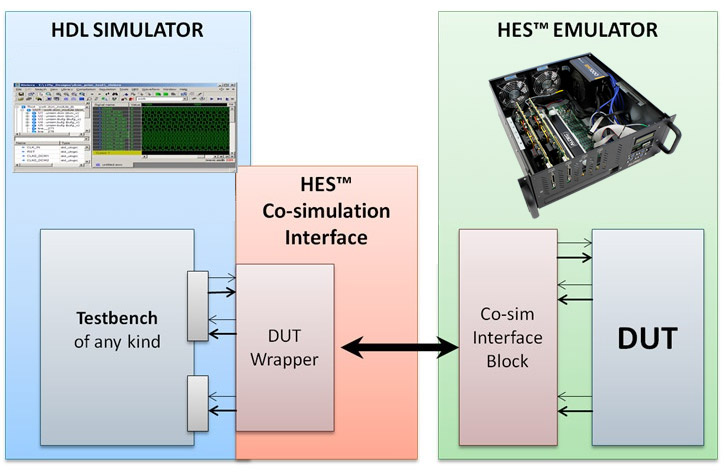

HESによるシミュレーションアクセラレーション

アルデックは長年にわたり、HES(Hardware Emulation Solutions)を提供してきました。その間、HESは最も高度なデザイン要求やお客様の要望に対応できるように進化してきました。シミュレーションアクセラレーションは、HESの使用方法の一例に過ぎません[2]。さらに2つの使用モデルに分かれています:

-

信号レベル、サイクルアキュレート

-

トランザクションレベルで、時間制限が緩い、または時間制限がない

このアプリケーションノートでは、あらゆる種類のテストベンチで利用可能な前者のデモンストレーションを行います。ただし、トランザクションレベルのシミュレーションの場合、加速率が桁違いに高くなるためトランザクションレベルのテストベンチへの投資は高い投資効果が得られることに注意してください。

Figure 10. 信号レベルのシミュレーションアクセラレーション

アルデックはDVMツールを提供し、HESボードのデザインコンパイルとインプリメンテーションの全プロセスを自動化します。また、他EDAベンダとのシミュレーションアクセラレーションを可能にするために、様々なHDLシミュレータ用のコ・シミュレーションインタフェースライブラリも含まれています。しかしRiviera-PROとHESの組み合わせは同じベンダのツールであり、アルデックはRiviera-PROのシミュレーションカーネルでミリ秒ごとにスクイーズするダイレクトフックを開発できるため、速度が最適化されています。他のベンダのシミュレータは、標準のPLI/VHPIインタフェースでサポートされています。

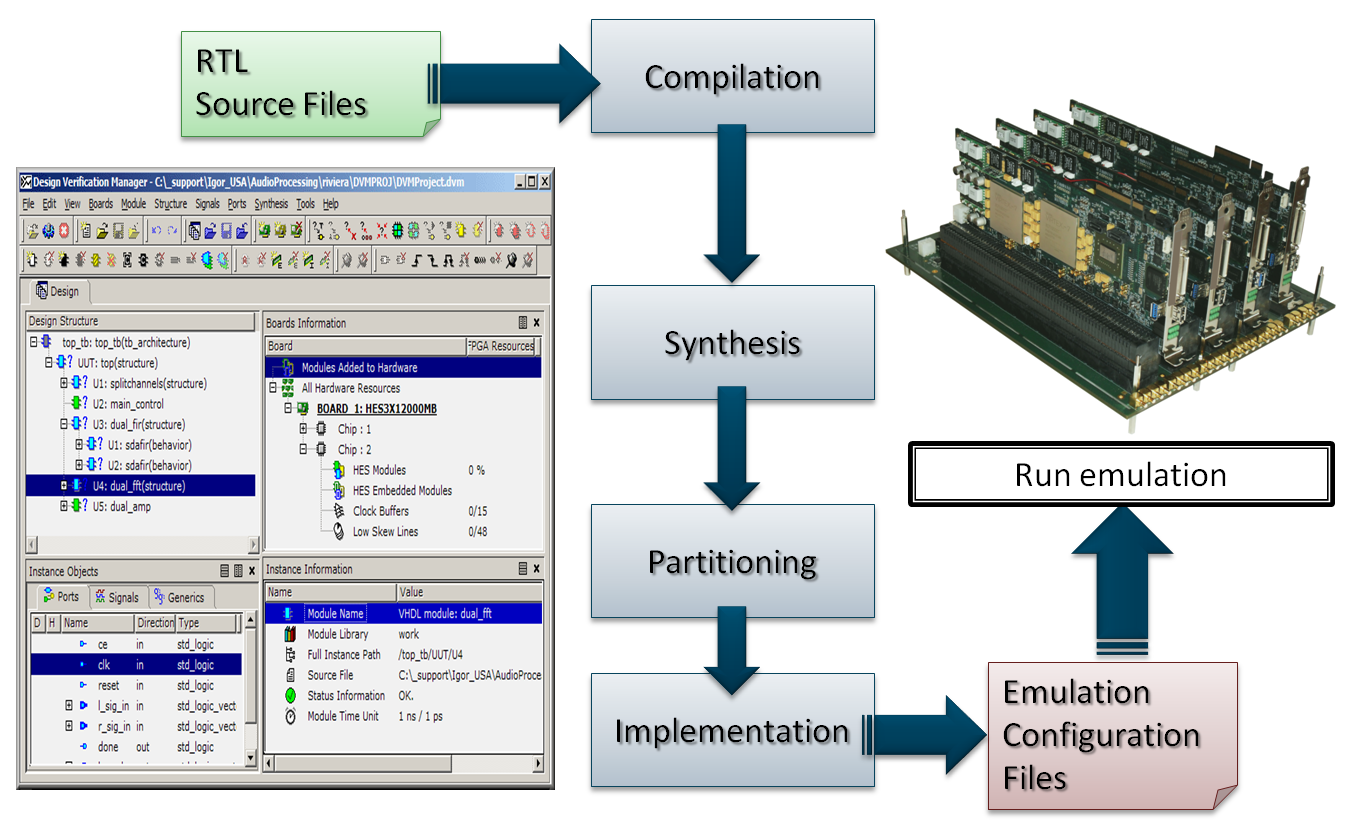

HES-DVMのデザインセットアップフロ

シミュレーションアクセラレーションのためのデザインセットアップフロー(図11)は、Vivado合成およびインプリメンテーションユーティリティーと

統合されたDVMツールによって完全に自動化されています。

図11. DVM™を使用したアクセラレーションのデザインセットアップフロー

DVMには多くの機能があり、現在のサンプルデザインで使用されている機能は次のとおりです:

-

VHDLおよびSystemVerilogのサポート - あらゆる種類のデザインのコンパイルが可能

-

EDIFネットリストのサポート - Vivado out-of-contextの合成で再利用

-

外部メモリ - 大きなメモリ(DDRなど)を外部オフチップメモリにマッピング

DVMセットアップフローの結果は、以下を含むファイルのセットです:

-

HES(この場合はVerilog)に追加されたモジュール/デザインのHDLラッパ

-

FPGAビットファイル(fpga_*.bit)

-

シミュレーションスクリプト(Simulate_HES.do)

-

ハードウェア信号とデバッグ構成をマッピングするための他ファイル

HESボードはシミュレータとシームレスに統合されています。PCI Expressインターフェースを介してホストワークステーションに接続します。アルデックは、必要なすべてのドライバとHDLシミュレータインタフェースを提供します。シミュレーションアクセラレーションの実行は、生成されたシミュレータスクリプト(Simulate_HES.do)を実行するだけで簡単に行うことができます。

アクセラレーション用のXilinxデザインの準備

アクセラレーションのためのデザインセットアップの詳細を確認しましょう。ここでは、Xilinx Vivadoデザインスイートで作成されたデザインに固有の手順を確認します。

デザインのコンパイル

Riviera-PROを使用する場合を除き、すべてのデザインとライブラリのソースをDVMでコンパイルする必要はありません。ここでは、VivadoのOOC(Out-of-Context) コンパイルフローを利用して、デザイン内でインスタンス化された各IPを個別に合成します。

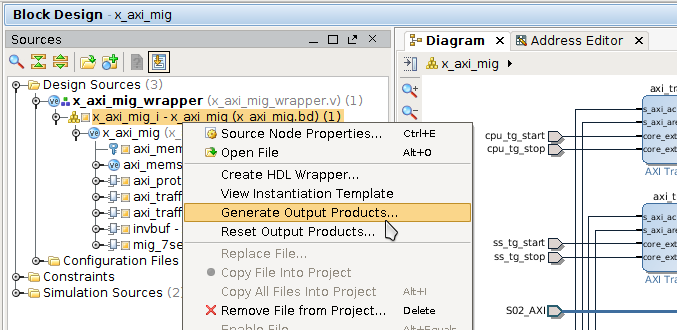

ブロック図が完成して検証したら、図12に示すようにブロック図ソースファイルのドロップダウンメニューにある"Generate Output Products..."オプションを使用してOOCファイルを生成できます。

図 12. VivadoのGenerate Output Products

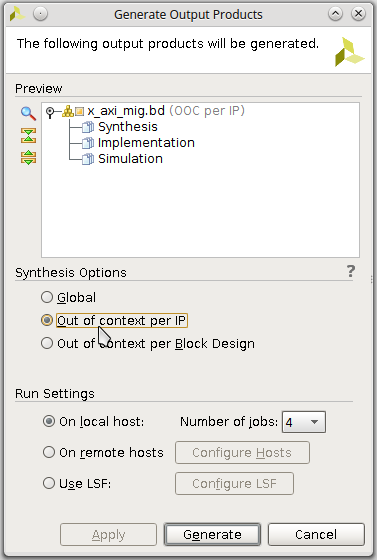

"Generate Output Products"ポップアップウィンドウには、"Out of context per IP"というオプションがあり図13のように選択します。この方法で生成された出力製品には、DVMセットアップフロー内で対象となる2種類のファイルが含まれています。これらは:

-

Verilogスタブファイル。各IPのブラックボックスソースで、名前に"_stub "という接尾辞が付いています(*_stub.v)。

-

シンセシスチェックポイント (*.dcp)。合成されたネットリスト (EDIF ファイル) を含むアーカイブです。

図 13. VivadoでOut of Context プロダクトの生成

必要なIPスタブとdcpチェックポイントは、Vivadoプロジェクトのsourcesディレクトリにあります。 例えば:

./x_axi_mig.srcs/sources_1/bd/x_axi_mig/ip/

各IPは別ディレクトリに格納されており、それぞれのスタブやDCPファイルはLinuxのfindコマンドで見つけることができます:

find *.srcs/ -type f -name "*_stub.v" find *.srcs/ -type f -name "*.dcp"

IPスタブファイル以外にも、ブロック図やVivadoプロジェクトに追加されたカスタムHDLソースファイルから生成されたすべてのラッパをコンパイルする必要があります。

Xilinx MIGラッパの準備

XilinxのメモリインターフェイスジェネレータIPはDVMツールで他IPとは異なる方法で処理されます。 DCPチェックポイントからEDIFネットリストを使用する代わりに、DVMツールで提供されるAXIインターフェイスを備えた外部メモリモデルにマップします。このようなマッピングの利点は、Xilinx MIGがオンボードDDR3メモリにすでに接続されている複合DDRコントローラに置き換えられることです。

DVMライブラリのメモリモデルは純粋なAXIスレーブインターフェイスのみを提供するため、他のAXI以外の信号の動作をエミュレートする適切なラッパを作成する必要があります。 MIGスタブソースファイルから始めて、必要な機能を実現するように変更すると便利です。 MIGスタブには下記インタフェースとポートが含まれています:

|

インターフェイスまたはポート |

プレフィックス |

備考 |

|

AXI Slave |

s_axi_* |

アルデックAXIスレーブラッパに接続する必要があります |

|

DDR |

ddr_* |

出力は接続したままにし、双方向バスは接続しないままにする必要があります |

|

APP Interface |

app_* |

これらは未使用の出力で、Lowに固定することができます |

|

OUT: ui_clk |

最も単純な実装は、入力クロックsys_clk_iのパススルーにするだけです。より正確にはゲートされた入力クロックsys_clk_iとしてモデル化することができ、ゲート信号はsys_rstがHighになった後の何サイクルか後にui_clkを有効にします |

|

|

OUT: ui_clk_sync_rst |

このシステムリセット出力は、アクティブHighです。sys_rstがLowにアサートされたときにHigh状態で始まり、sys_rstがHighになってから数サイクル後にディアサートされます |

|

|

OUT: mmcm_locked |

Xilinx MIG内でMMCMキャリブレーションが完了したことを示します。 sys_rstのアサート解除からしばらくすると、Highがアサートされます |

|

|

OUT: init_calib_complete |

DDRラインのキャリブレーションが完了したことを示します。 この信号は、mmcm_lockedのしばらく後にHighにアサートされます |

注意:MIGコントローラ用のエミュレーションラッパのリファレンス実装は、HES-DVMソフトウェアに同梱されているサンプルプロジェクト内にあります。

Xilinx IPのEDIFネットリストの再利用

すべてのソースがコンパイルされ、DVMツールでデザインが作成されると、次の段階として図11に示すように合成が実行されます。合成を開始する前にブラックボックススタブとしてコンパイルされたすべてのXilinx IPにEDIFネットリストを設定する必要があります。このようなEDIFネットリストは、通常のZIPアーカイブであるDCPチェックポイントファイルに含まれていることがわかりました。DCPからEDIFネットリストを抽出するためには、標準的なZIP Packerプログラムを使用できます。EDIFファイルのベースネームはDCPと同じで拡張子は.edfです。例えば、AXIクロスバーIP用に生成されたDCPファイルは、"x_axi_mig_xbar_0.dcp"となります。

EDIFネットリストは、Linuxでは以下のコマンドで抽出できます:

unzip x_axi_mig_xbar_0.dcp x_axi_mig_xbar_0.edf

DVMではデザイン構造内からこのモジュールのインスタンスを見つけ、抽出されたネットリストを使ってEDIFとして設定します。

MIGラッパを外部メモリとしてマッピング

Xilinxの他IPコアとは異なり、MIGはEDIFとして設定するのではなく、外部メモリにマッピングする必要があります。DVMは外部メモリモデルのライブラリを提供しており、そのうちの1つはAXIスレーブのインタフェースを持っています。このモデルをMIGラッパに使用する必要があります。

DVMの外部メモリモデルを使用することの利点は、デバッギングインタフェースを提供することでシミュレーションの実行時にメモリの内容確認、変更を行うことができることです。

アクセラレーションのベンチマーク

ベンチマークのために、テストベンチは以下のように編成しました:

-

シミュレーションを開始し,DDR3コントローラの初期化とキャリブレーションを待つ

-

AXIトラフィックジェネレータの起動

-

AXIポートS02_AXIで200の書き込みおよび読み取りバースト転送を生成(各バースト転送長は64です。つまり、テストベンチはメモリサブシステムから100KBのデータを読み書きします)

同じテストシナリオを、Riviera-PROによる純粋なシミュレーションとHESによるアクセラレーションシミュレーションで行いました。両方のシミュレーションで実行時間を測定しました。

|

Riviera-PRO |

Riviera-PRO + HES |

|

|

実行時間 |

1537 秒 |

3 秒 |

|

加速率 |

512 |

ベンチマークに使用したワークステーションとソフトウェア:

ワークステーション:

|

Component |

Value |

|

CPU |

Intel® Core™ i7-3770K CPU @ 3.50GHz |

|

RAM |

32 GB |

|

HES Board |

HES7XV4000BP_REV2, contains 2x Virtex-7 2000T FPGAs |

ソフトウェア:

|

Component |

Value |

|

OS |

Linux CentOS 6, x86_64 |

|

Simulator |

Riviera-PRO 2017.02 |

|

Design env |

Vivado 2016.4 |

|

Acceleration env |

HES-DVM 2017.02 |

まとめ

シミュレーション技術は、デザインゲート数の増加に比例して拡張されないため設計検証プロセスにおける真のボトルネックとなっています。シミュレーションに時間がかかることは、大規模FPGAデザインでも経験したことがあります。Xilinx Vivadoは非常に強力な設計環境と、すぐに使用できるIPコアの豊富なライブラリを提供しています。しかし、RTLやゲートレベルのネットリストをベースにしたシミュレーションモデルは、暗号化されていることが多く、シミュレーションに時間がかかります。

このアプリケーションノートでは、シミュレーション速度が大幅に改善されることを実証するベンチマークを行いました。通常はデザイン全体のごく一部である小さなメモリサブシステムをHESでシミュレーションすることで、FPGAベースのシミュレーションアクセラレーションの大きな可能性が見えてきます。しかし成功の鍵は、デザインセットアップの自動化とFPGAボードとシミュレータをいかに簡単に接続するかにあります。アルデックは長年にわたり、この分野でのリーディング・ポジションを確立してきました。高いレベルの自動化と主要なHDLシミュレータとのシームレスな統合を実現しています。

リファレンス

[1] Xilinxはトレーニングおよびチュートリアルビデオの豊富なリソースを提供しています。 詳細についてはXilinx ウェブサイトにアクセスしてください

[2] 詳細についてはアルデックのウェブサイトにアクセスしてください:https://aldec.com/jp/solutions/hardware_emulation_solutions

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.