Intel Quartus II からの Active-HDL 実行方法

はじめに

Intel® Quartus ソフトウェアからActive-HDL をNativeLink 機能を使用して直接実行できます。このアプリケーションノートでは、 Intel Quartus II のNativeLink 機能の使用方法について説明します。なお、Active-HDL 10.3 と Intel QuartusII 16.1 で確認を行っています。このインタフェースは、デフォルトのシミュレータとしてActive-HDLを使用し、VHDL, Verilog, SystemVerilog(”デザイン”構文)混在シミュレーション実行を行うことが可能です。

Quartus II でActive-HDL のコンフィギュレーション

-

Intel Quartus II でデザインを開き、全てのソースファイルをコンパイル

-

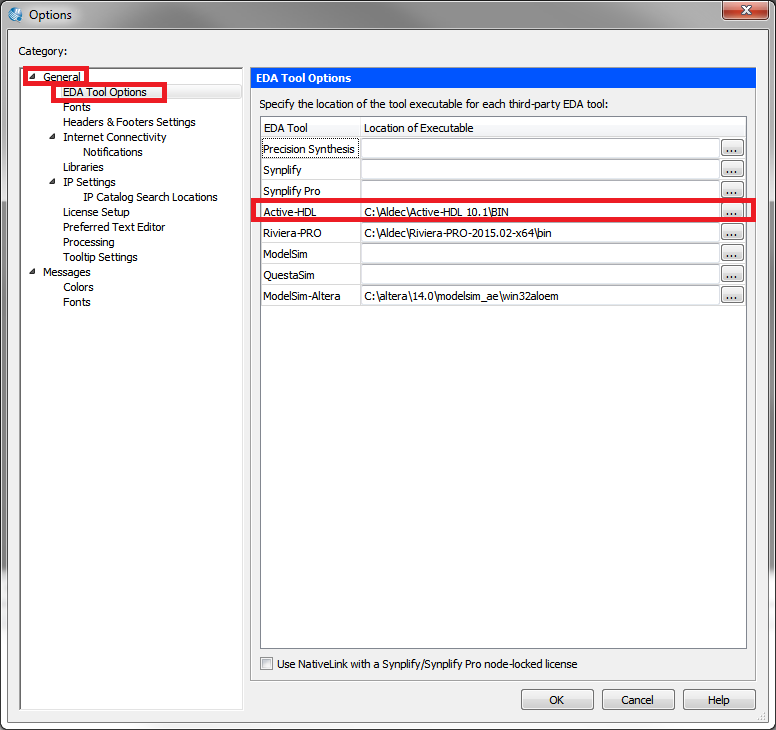

Quartus IIでTools | Options を使用し、Options ウィンドウを開きます。General カテゴリ内のEDA Tools Options を選択します. Active-HDL エントリ内で、Active-HDL インストール内の\bin フォルダへのパスを選択します。

Figure 1 EDA Tool Options

-

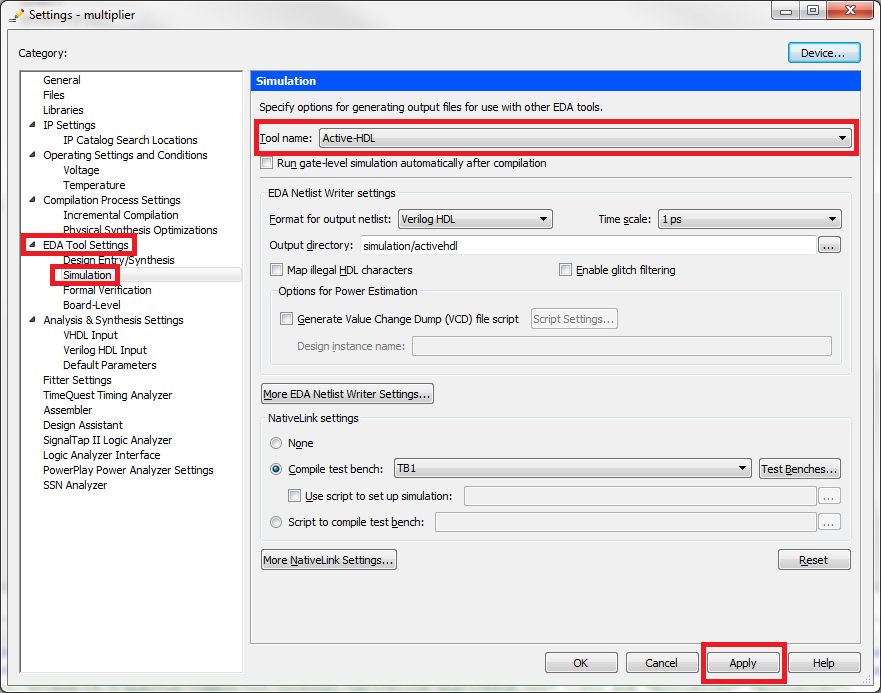

Assignments | Settings メニューに移動します。ここで、EDA Tool Settings 内のSimulation カテゴリを選択します。右側にあるTool name ドロップダウンボックスで、figure 2 にあるようにActive-HDL を選択しApply をクリックします。

Figure 2 Quartus II のEDA Tool Settings

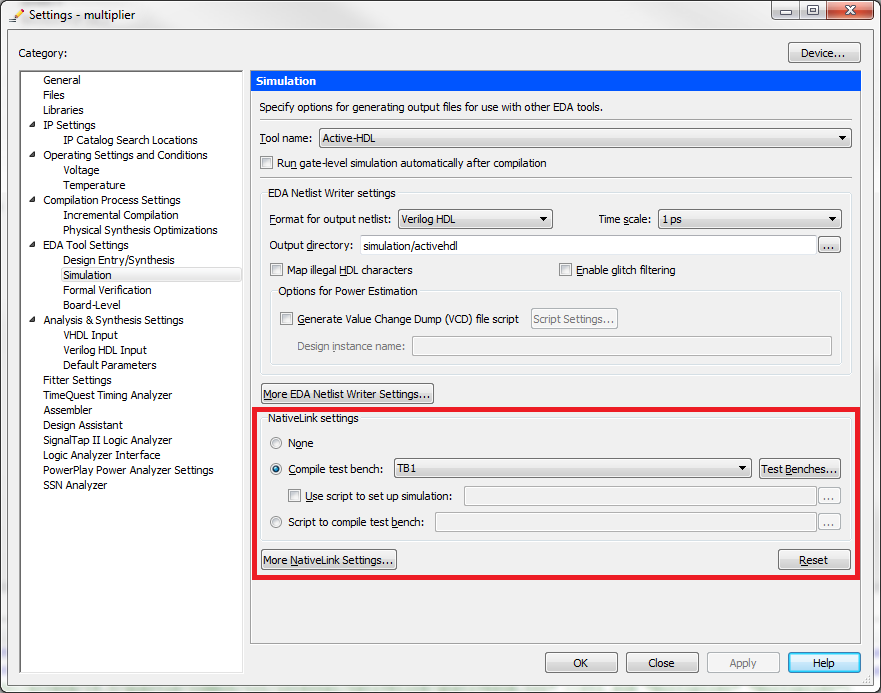

NativeLink の設定

NativeLink 設定は、Figure 3にある様に右側にあるSimulation カテゴリの下部にあります。シミュレーション用のテストベンチの設定として3つのNativeLink 設定があります。

-

None — テストベンチオプションをオフにします。Active-HDL が開いた際、テストベンチを追加し、それをコンパイルし手動でシミュレーションを実行する必要があります。その他のプロジェクトファイルは自動的にActive-HDL に追加されます。

-

Compile test bench — 1つ以上のテストベンチを作成した場合、シミュレーション中にコンパイルされたテストベンチを選択することができます。

-

Use script to set up simulation — Active-HDLで、 シミュレーション実行用のコマンドを含むスクリプトを指定することが出来ます。この場合、Acrive-HDL 起動時、テストベンチをコンパイル、およびシミュレーション用のコマンドを含むスクリプトが呼び出され実行します。

Figure 3 EDA Tool Settings

NativeLink 設定から自由にオプションを選択できます。シミュレーションの実行については、次のセクションを参照してください。これらのオプションの詳細については、このアプリケーションノートの最後にあるリンクをクリックしてください。

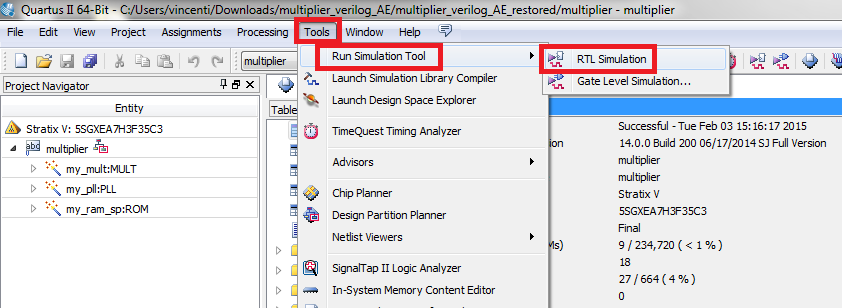

シミュレーションの実行

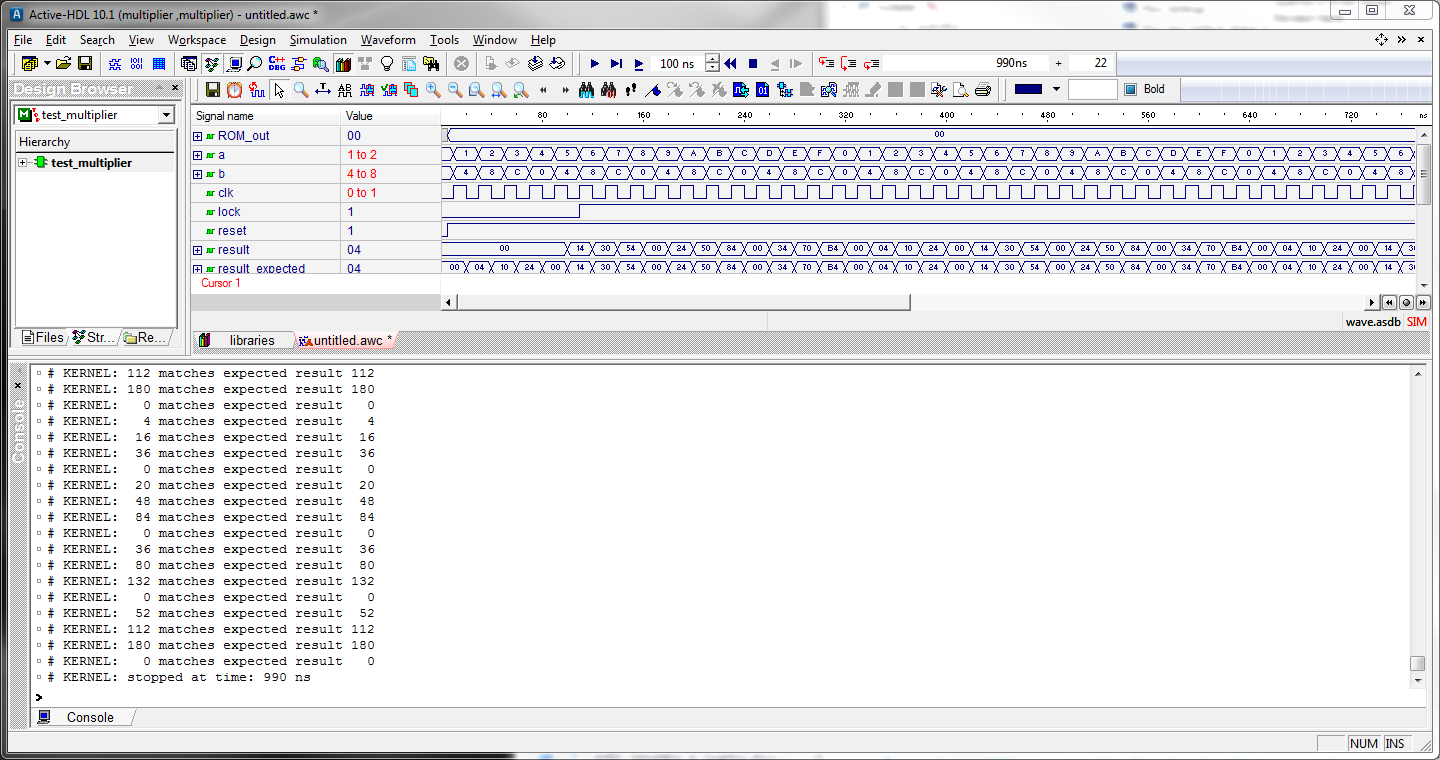

Quartus II からActive-HDL を起動するには,Tools | Run Simulation Tool | RTL Simulation option をクリックします。 Active-HDL は起動し、プロジェクトの作成、および必要なファイルをプロジェクトに追加します。また必要な Intel ライブラリをコンパイルします。波形に信号を追加し、その後にシミュレーションを実行します。Figure 4 の様にシミュレーション終了時、コンソールにシミュレーションの終了メッセージを表示します。

Figure 4 シミュレーションの実行

Figure 5 シミュレーションの実行

さらに詳しい情報

Quartus IIソフトウェアからActive-HDLシミュレータの起動と実行の詳細に関しては、http://www.altera.com/literature/hb/qts/qts_qii5v3.pdf をご覧ください。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.