Xilinx AXIベース IPの概要

はじめに

このドキュメントでは、最新世代のAMBA®(Advanced Microcontroller Bus Architecture)インターフェースであるAXI4(Advanced eXtensible Interface)インターコネクトプロトコルファミリについて説明しています。

AXIバスファンクションモデルの概要

SoC(System-on-a-Chip)で非常に重要なのは搭載するブロックだけでなく、それらをどのように相互接続するかということです。AMBAは10年以上前からSoC設計のオンチップバスとして広く使用されています [1]。1996年にARM®によって導入されて以来、このインターフェースの範囲はマイクロコントローラデバイスをはるかに超えており、現在の携帯型モバイルデバイスで使用されるプロセッサを含む幅広いASICおよびSoC部品の事実上の標準となりました。AMBAインタフェースは、第1世代ではASB(Advanced Systems Bus)とAPB(Advanced Peripheral Bus)、第2世代ではAHB(High-performance Bus)、第3世代ではATB(Advanced Trace Bus)とAXIを導入し、シングルチップ上のロジック密度の増加に伴い、より高性能の相互接続要求に対応してきました。

現在のSoCでは、複数のクラスタや高度なペリフェラルが搭載されているため、相互接続ファブリックが大きなボトルネックとなっています。これまでの相互接続プロトコルでは、増大し続けるコンピューティングパワーに対応できず、適切な帯域幅も確保できませんでした。そのため、XilinxはARMと緊密に協力し、AMBAインターフェースの第4世代であるAXI4を定義しました。AXI仕様は、定義されたシグナリング規格を使用してIP間でデータを移動するためのプロトコルを定義するフレームワークを提供します。この規格によりIPが相互にデータを交換でき、システム全体でデータを移動できることを保証します [2]。AXIプロトコルは、データの交換、転送、および変換の方法を定義し、効率的で柔軟性が高く、予測可能なデータ転送手段も保証します。

XilinxはAXI4への取り組みの一環として、7シリーズ、Spartan-6、Virtex-6、および今後のデバイスファミリの次世代IP相互接続規格として採用しました。

この移行プロセスは、現在のXilinxを中心としたSoC設計手法とフローが、新しい半導体業界標準のプラグアンドプレイIPによって拡張されたことを明確に示しています。使用可能なAXI4の機能概要と、AXIオプションで置き換えられるプロトコルの一覧を表1に示します。

|

表 1. AXI機能の可用性とIPの置き換え |

|||

|

インタフェース |

適用性 |

機能 |

置き換え |

|

AXI4 |

高性能のメモリマップド要件 |

|

|

|

AXI4-Lite |

シンプルで低スループットのメモリマップド通信 |

|

|

|

AXI4-Stream |

高速ストリーミングデータ |

|

|

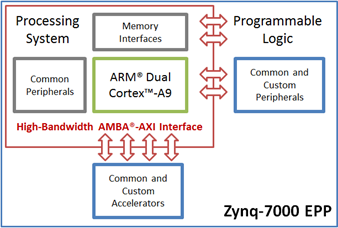

Artix-7、Kintex-7、Virtex-7 などの最新のザイリンクス 28nm FPGA は AXI4 インターフェイスをサポートしているだけでなく、Zynq™-7000 EPP も AXI4 インターフェイスをサポートしており (図 1)、デバイスに依存しない IP の開発が可能になっています。(Zynq EPPは、業界標準のARM®デュアルコアCortex™-A9 MPCore™プロセッシングシステムとXilinx 28nmプログラマブルロジックを組み合わせた新しいクラスの製品です)。

図 1. ZynqEPPにおけるAMBA-AXI相互接続の役割

Zynq-7000 EPPの価値は、ハードウェア(HW)およびソフトウェア(SW)の開発ツール、オペレーティングシステムなど、Zynq-7000ファミリをサポートするすべての要素によって高められます。アルデックツールを従来から使用しているハードウェアデザイナには、強力なZynqパートナーエコシステムの傘下で多くのメリットを利用できます:

-

評価、プロトタイピング、開発に利用できる複数のデザインプラットフォーム

-

直感的なデザインインターフェースによる迅速なシステム構成

-

AXIベースIPをドラッグアンドドロップすることでペリフェラル機能を容易に拡張可能

-

既存の実績のある豊富なIPの選択

-

システムレベルデバッグやプロセッシングシステムとプログラマブルロジック間のクロストリガ

-

AXIバス機能モデルによるカスタムペリフェラルの早期検証

メリット

7シリーズ、Virtex-6、およびSpartan-6ベースのデザインの市場投入までの時間の要件を満たすためにIPに依存しているお客様にとって、AXI4は単一の標準インターフェイスを提供し、IP の統合を容易にします。ISEはエンベデッド、DSP、およびロジックドメイン全体で単一のオープンスタンダードインタフェイスを備えたAXI4ベースIPの幅広いセットを提供します。AXIには以下のようなメリットをもたらします:

-

学習曲線の短縮 - AXI4は実際には統合されたインタフェースであるため、エンドユーザーはIPの標準プロトコルを1つだけ学習して知る必要があります。

-

統合コストの削減 - 業界標準を採用することで、異なるドメインから提供されるIPの統合、自社IPの開発、さらにはサードパーティのIPプロバイダとの連携が非常に容易になります。この規格に移行することで、Xilinx IPカタログだけでなく、ARMパートナーの世界的なコミュニティにもアクセスできるようになります [3]。

-

設計時間を短縮し、ターゲット市場向けに最も魅力的な製品を作ることができます。AXIは完全に仕様化され、パフォーマンスとスループットが最適化されているため、実際の設計工数は減少します。

アーキテクチャ

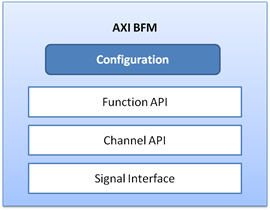

機能検証に関しては、バスファンクショナルモデル(BFM)がバスのスティミュラスを生成する機能を提供し、バスに接続するハードウェアコンポーネントの検証を簡素化します。AXI4用のBFMは、AXI4、AXI4-Lite、およびAXI4-Streamの各バージョンを含め、Cadence Design SystemsによってXilinx向けに開発されました [4] 。すべてのAXI BFMは、信号インタフェース、チャネルAPI、ファンクションAPIの3つの主要なレイヤで構成されています [5]。一般的なAXI BFMのアーキテクチャを図2に示します。信号インタフェースには、一般的なVerilogの入出力ポートとそれに関連する信号が含まれています。チャネルAPIは、AXIプロトコルに固有の基本的なトランザクションレベルで動作する定義済みのVerilogタスクで、リードアドレスチャネル、ライトアドレスチャネル、リードデータチャネル、ライトデータチャネル、ライトレスポンスチャネルが含まれます。

図 2. AXI BFM アーキテクチャ

この分割により、各チャネルに関連付けられたタスクを同時または順次実行することができます。これにより、テスト作成者は、順不同の転送やインターリーブされたデータ転送などの機能を制御し、実装することができます。ファンクションレベルのAPIは、完全なトランザクションレベルの制御が可能で、たとえばAXIリードバーストプロセス全体が1つのVerilogタスクにカプセル化されます。テスト作成者は、このAPIレイヤを使用して、チャネル順序付けに関するAXI4の仕様に準拠していることを確認することが推奨されます。AXI BFMアーキテクチャの最後の重要な要素として、コンフィギュレーションメカニズムがあります。これはVerilogのパラメータやBFMの内部変数を使用して実装され、シミュレーション時にアドレスバス幅やデータバス幅などのパラメータ、つまりコンフィギュレーション変数を設定するために使用されます。

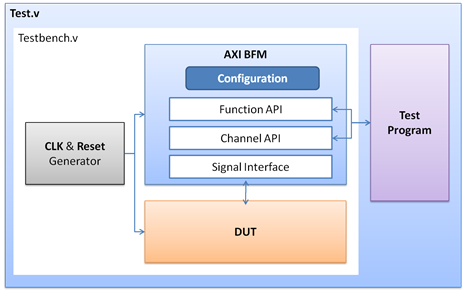

図 3. AXI BFM の使用方法

AXI BFMの使用目的を図3に示します。テストベンチには、AXI BFMの複数のインスタンスを含めることができます。DUTとBFMは、クロックとリセットジェネレータを含むテストベンチにインスタンス化されます。次にテスト作成者は、テストベンチをテストモジュールにインスタンス化し、BFMのAPIレイヤを使用してテストプログラムを作成します。テストプログラムは、forkやjoinを使用してAPIタスクを順次または同時に呼び出します [6].

まとめ

AXI4プロトコルが利用可能になったことで、ARMおよびCortexプロセッサは高性能SoCの分野で競争力を維持し続けています。最近ではXilinxが、

Zynq™-7000ファミリのEPP(Extensible Processing Platform)製品をはじめとする、現在および将来のデバイスファミリや製品 [7] にAXI4を採用したこともあり、主要なシリコンベンダの最新デバイスファミリでの利用や、AXIベースIPの幅広いポートフォリオを利用するためには、すべてのSoCデザイナがこのプロトコルを習得することが不可欠となっています。主要なEDAベンダが採用したことで、AXI4ベースのシステムデザインを構築するための強力なエコシステムが確立され、生産性の向上と市場投入までの時間短縮につながります。

参考文献

-

[1] AMBA Open Specifications – http://www.arm.com/products/system-ip/amba/amba-open-specifications.php

-

[2] AXI Reference Guide – http://www.xilinx.com/support/documentation/ip_documentation/axi_ref_guide/v13_4/ug761_axi_reference_guide.pdf

-

[3] ARM Community Partners - http://www.arm.com/community/partners/all_partners.php

-

[4] AXI Bus Functional Model – http://www.xilinx.com/products/intellectual-property/DO-AXI-BFM.htm

-

[5] AXI Product Brief – http://www.xilinx.com/support/documentation/ip_documentation/cdn_axi_bfm/v1_9/pb001_axi_bfm.pdf

-

[6] DS824, AXI Bus Functional Model Data Sheet (practical examples of test programs and test bench setups)

-

[7] Zynq-7000 Extensible Processing Platform Summary – http://www.xilinx.com/support/documentation/user_guides/ug804_zynq-7000_plat_sum.pdf

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.