Xilinx ISE からの Active-HDL 実行方法

1 はじめに

本ドキュメントでは、Xilinx ISE Project Navigator から Active-HDL を起動し、VHDL/Verilog/SystemVerilog のビヘイビィアおよびタイミングシミュレーションを実行する方法について説明します。Active-HDL 8.3/8.3sp1 以降とXilinx ISE 12.1 以降に対応しています。

2 Active-HDL の設定

2.1 Active-HDL 起動ファイルの自動インストール

Xilinx ISE Project Navigator から Active-HDL を実行するためのファイルセットが、Active-HDL インストール時に自動インストールされます。ISE Project Navigator からActive-HDL を起動すると、Active-HDL 8.3/BIN/xilnx_ise.bat が実行され、Active-HDL ワークスペースとデザインが作成され、シミュレーションに必要なファイルが付加されます。

2.2 ザイリンクスシミュレーションライブラリのインストール

ザイリンクスのモデルやIP コアを含むデザインをシミュレーションするには、ザイリンクスシミュレーションライブラリが必要になります。Active-HDL では、コンパイル済ライブラリをツールとあわせて提供しています。お使いになるライブラリがインストールされていることを、Active-HDL のLibrary Manager で確認してください。

必要なライブラリがインストールされていない場合には、アルデックのウェブよりダウンロードしてください。

3 ISE Project Navigator の設定

3.1 Pereferences の設定

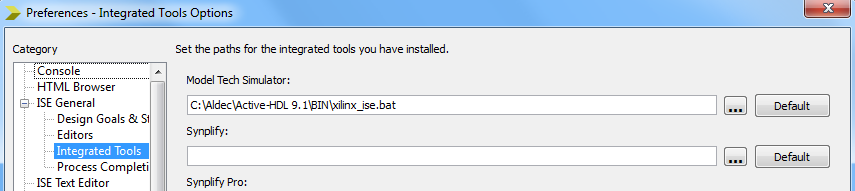

After ISE Project Navigator でプロジェクトを開きます。メニューからEdit→Preferences を選択し、Preferences ウィンドウを開きます。Category → ISE General → Integrated Tools を選択し、右ペインのModel Tech Simulator 欄にて、Active-HDL インストールディレクトリ¥BIN¥xilnx_ise.bat を指定し、OK ボタンをクリックし Preferences ウィンドウを閉じます(図1)。

図1

3.2 Design Properties の設定

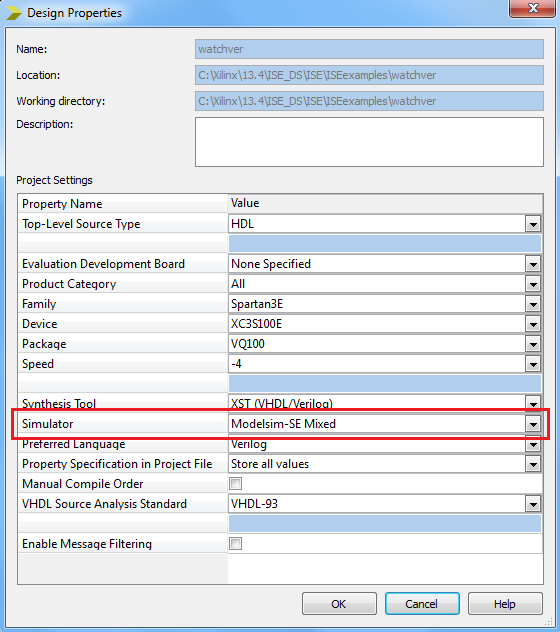

メニューからProject→Design Properties を選択し、Project Settings のSimulator から、ModelSim の任意のエディションを指定して、OK ボタンをクリックしてください(図2)。

図2

3.3 Process Properties の設定

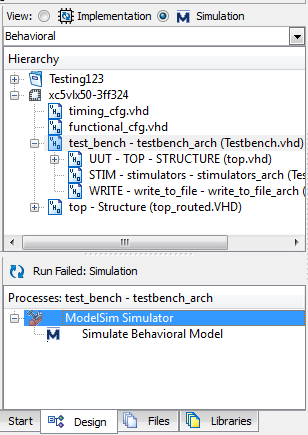

Project Navigator の View にて、Simulation をチェックし、Behavioral を選択します(図3)。

図3

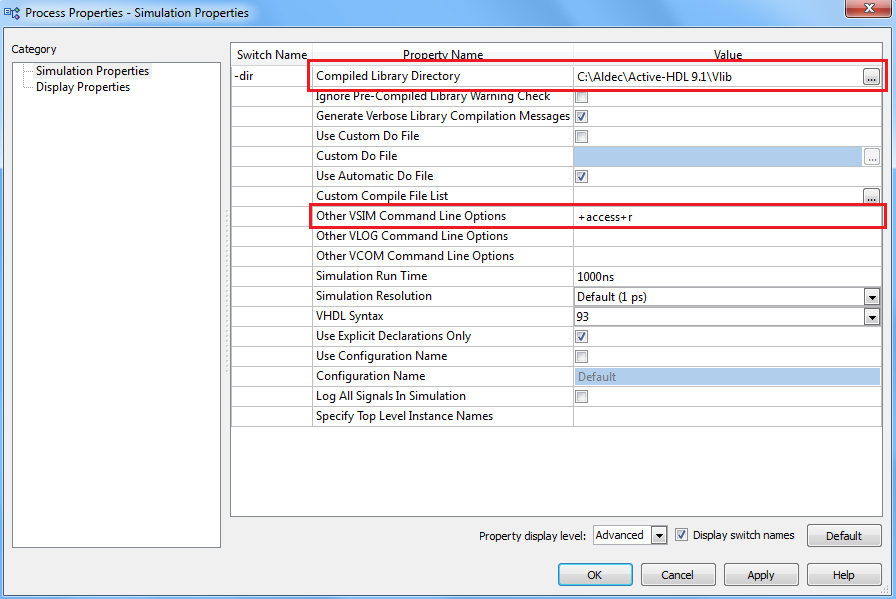

メ ニューからProcess→Properties を選択し、Process Properties ウィンドウを開きます。Category のSimulation Properties にてProperty display level リストボックスからAdvanced を選択し、次の設定をします(図4)。

●Compiled Library Directoryを Active-HDLインストールディレクトリのVlibに変更します。

●Ignore Pre-Compiled Library Warning Check をチェックします。

Active-HDL はコンパイル済みの Xilinx ISE ライブラリをツールと合わせて提供しています。

●Other VSIM Command Line Options に、+access +r を設定します。

図4

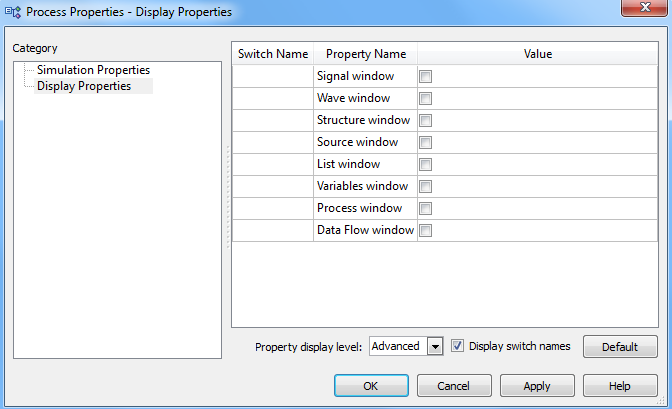

続いて、Category のDisplay Properties にて全てのチェックをはずし、OK ボタンをクリックします(図5)。

図5

4 ISE Project Navigator からのActive-HDL の実行

4.1 Active-HDLの起動

Processes ウィンドウのDesign タブにて、Simulate Behavioral Model のマウス右ボタンメニューからRun を選択します。

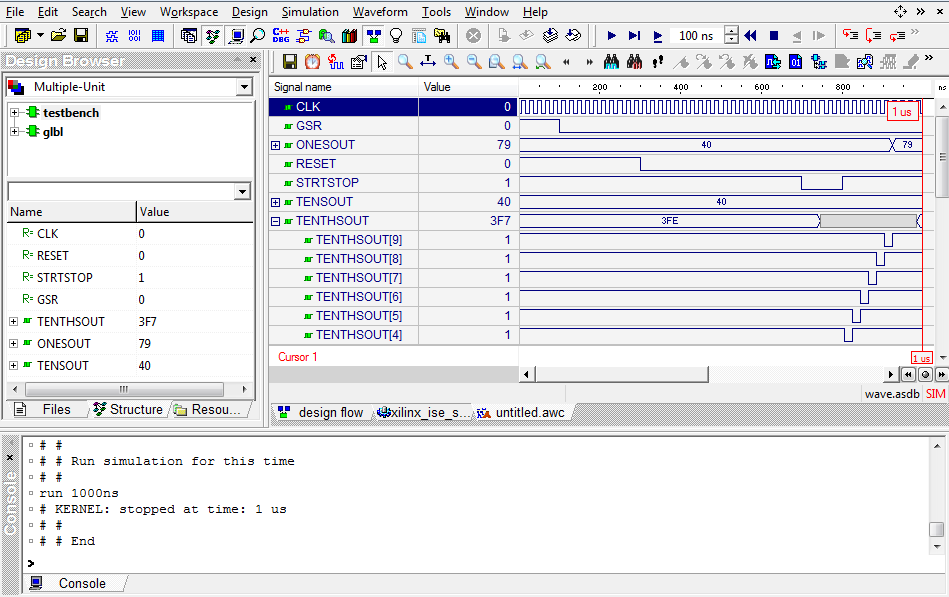

Active-HDL が起動し、Design Browser Files タブに次のファイルが付加され、スクリプトファイル.fdo が自動実行されます(図6)。

● シミュレーションン対象のHDL ソースファイル

●ISE が生成した、コンパイルおよびシミュレーション実行用のスクリプトファイル(.fdo)

デザインファイルのコンパイルに続いて、イニシャライズシミュレーションが実行され、Structure タブにデザインの階層構造が表示されます。

図6

5 タイミングシミュレーションの実行

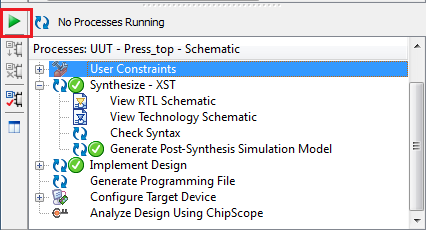

タイミングシミュレーションを実行するには、Project Navigator の View を Implementationに切り替えます(図7)。

![]()

図7

-

Implement Top Moduleボタンを押すか、トップレベルモジュールを右クリックしてImplement Top Moduleを選択し、論理合成と配置配線を実行します(図8)。

図8

-

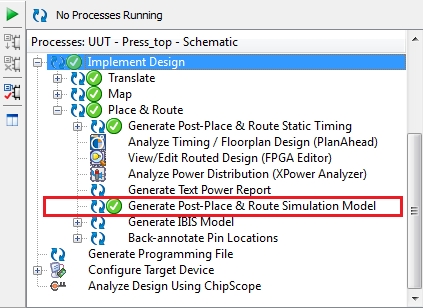

Implement Design を展開して、Post-Place & Route シミュレーションモデルを生成します(図9)。

図9

-

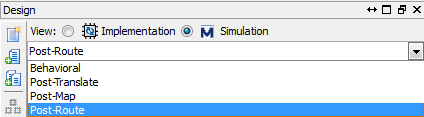

view を Simulation に変更し、Behavioral かた Post Routeに変更hします(図10)。

図10

-

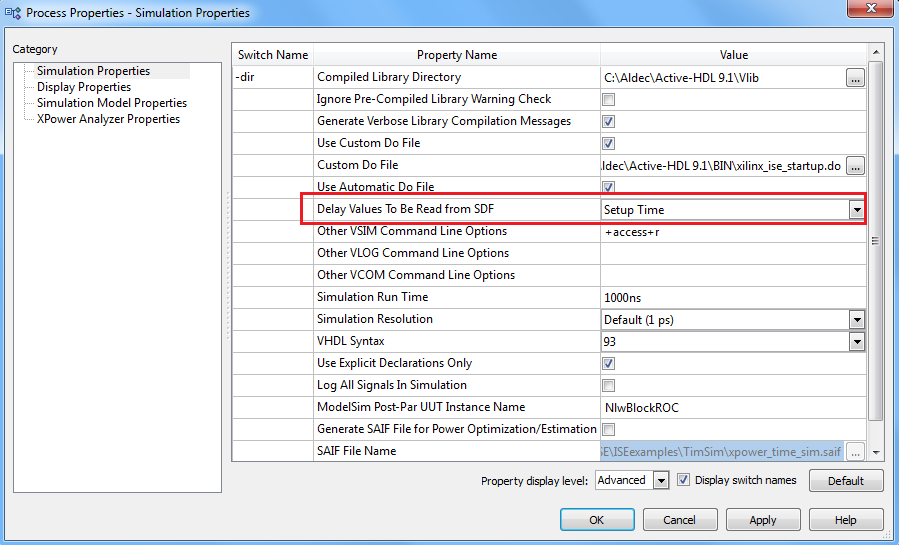

processes ウィンドウで Simulate Post-Place & Route Model を右クリックして、Process Propertiesを選択します。

-

Delay Values To Be Read from SDF欄が追加されていることがわかります(図11)。

図11

-

Display Properties は、Behavioral シミュレーションと同じにします。

-

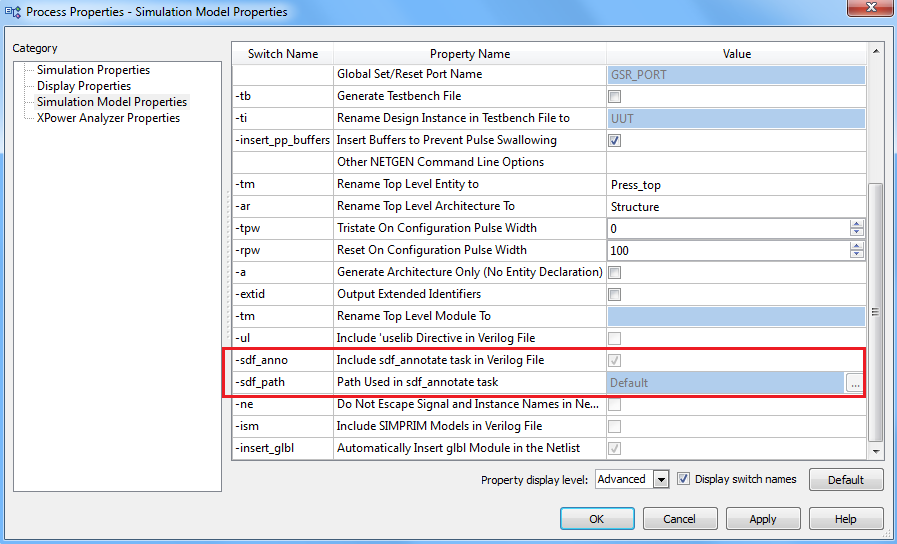

Simulation Model Properties でも、タイミングシミュレーション用の -sdf スイッチを確認できます(図12)。

図12

-

Simulate Post-Place & Route Modelを右クリックして run を選択することにより、タイミングシミュレーションを実行します。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.