ALINTでのFPGAプリミティブのネイティブサポート

概要

高性能デザインルールチェッカ (DRC) は、自前の合成エンジンで大規模なチップレベルのデザインルールチェックに必要な情報を取得します。しかし、一般的な合成手法では合成できないコードを持つFPGAベンダのコンポーネントやプリミティブには効果がありません。ALINTはユニークな方法(Xilinx®とAltera®の提供するライブラリでもっともよく使用されるものをネイティブサポート)でこの問題を解決しています。このアプリケーションノートではその仕組みについて説明します。

ベンダライブラリの中味

FPGAのスケマティックライブラリに含まれるシンボル (コンポーネントとも呼ばれる) は次の種類があります。

-

プリミティブ:インプリメントツールに直接認識されるリソースで、通常はターゲットFPGAのロジックリソース (I/Oピン、バッファ、論理ゲート、フリップフロップなど) に対応します。

-

マクロ:プリミティブと別マクロで構成され、やや複雑な機能 (カウンタ、シフトレジスタ、デコーダなど) を実装できます。マクロには2種類あり、ソフトマクロは所定の機能を実現していますが物理的実装にはインプリメントツールが必要になります。ハードマクロは、マッピングと配置情報が決まっいて実装は最適化されています。

通常、FPGAライブラリはプリミティブとマクロを幅広くサポートしています。もっとも単純なものはバッファや2入力ゲートで、複雑なものとしてはアキュムレータやRAMなどがあります。

一般的な合成とFPGAプリミティブのネイティブサポートの比較

一般的な合成手法では、合成できないコードを持つベンダコンポーネントには効果がありません。コンポーネントを適切なロジックリソースに実装するのはソフトウェアインプリメントツールの役目です。通常の合成では、ベンダコンポーネントはブラックボックスとして扱われるため、次のような問題が発生します。

-

色々なルールで違反の誤検出がレポートされます (例えば、ブラックボックスI/Oへの接続チェック、または外部入力ポートからの制御性に関する問題の検出、組み合わせフィードバックの解析などのルール)。

-

デザイン階層に関する情報が不完全なままになります。チップレベルのルールでデザイン要素同士の相互接続を正しく解析できず、デザインの問題が未解決のまま残る場合があります。

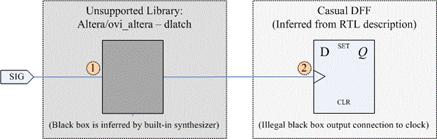

一般的な合成方法について図1に示します。

-

ポイント1: SIG信号はブラックボックスの入力に接続されています。この信号はデザインの他ブロックに伝搬しません。そのため、信号がクロックまたはリセットとして使われていたとしても、そのような信号として認識されません。これによりルール違反の漏れまたは誤検出につながります。

-

ポイント2: ブラックボックスの出力はフリップフロップのクロックピンに接続されています。不適切なクロック源として誤検出される可能性があります。

図1: 一般的な合成手法

ベンダコンポーネントを正しく扱うには、リントツールが内部の構造と機能を認識できなければなりません。内部構造が判断できれば、ベンダコンポーネントを等価のモデルに置き換えて合成し、ブラックボックスの生成を避けることができます。

ベンダコンポーネントのサポートレベル

ベンダライブラリのコンポーネントは、内部構造をツールがどれだけ認識するかによって、サポートレベルが3段階に分かれます。

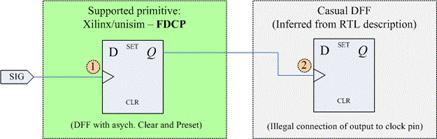

フル – ALINTはコンポーネントの内部構造 (インタフェースと内部ロジック – ホワイトボックス) を完全に把握しています。フルサポートされるプリミティブの扱いについては図2をご覧ください。

-

ポイント1: SIG信号は、サポートされているベンダプリミティブのクロックピンに接続されているためクロックとして自動検出されます。

-

ポイント2: フリップフロップの出力が別フリップフロップのクロックピンに接続されているという違反が検出されます。(プリミティブがサポートされず、ブラックボックスに関する違反が誤検出される場合とは違います)

図2: プリミティブのフル・ネイティブサポート

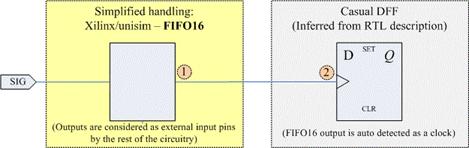

簡略 – 一部のプリミティブは内部構造が複雑で、等価の論理モデルで完全に置き換えることができません。FIFO, RAM, LUTなどが該当します。これらは、チップレベルのルールにおいてはグレーボックス (組み合わせ回路のフィードバック、クロック、リセットについては明白で特殊なブラックボックス)として扱われます。簡略サポートの一例を図3に示します。

-

ポイント1: FIFO16の出力はクロックとして自動的に検出され、それ以外のデザイン内でも正しく認識されます。

-

ポイント2: FIFO16の出力がフリップフロップのクロックピンに接続されているという、ブラックボックスに関する違反は検出されません。

図3: プリミティブの簡略ネイティブサポート

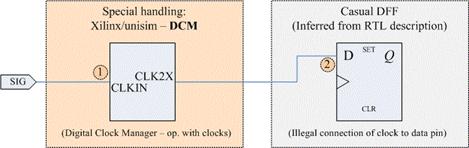

特殊 – 一部のプリミティブ、例えばクロックジェネレータ (DCM, PLL) やランダムアクセスメモリ (RAM) は等価の論理モデルで置き換えられませんが、ツールはその内部構造を認識する必要もありません。ただし、そのインタフェースは重要です。クロックジェネレータの出力はデザイン内ではグローバルクロックとして扱われ、その周波数の関係性も考慮しなければなりません。クロック出力を複数持つベンダプリミティブは複数のクロックドメインを推論する場合があります(DCMの入出力クロックも関して周波数と位相が一致しない場合、別々のドメインとして推論されます)。特殊サポートの一例を図4に示します。

図4: プリミティブの特殊ネイティブサポート

ALINTでのベンダプリミティブサポートの段階をまとめると次のようになります。

-

フル – ホワイトボックス

-

簡略 – グレーボックス

-

特殊 – インタフェースのみ

未サポートのプリミティブはブラックボックスとして扱われます。サポートしているライブラリの詳細は、ツールドキュメント (User's Guide | Advanced Features | FPGA Vendor Primitives | Supported Libraries) に掲載されています。次のベンダライブラリは完全にサポートされます。

-

Xilinx – unisim, ovi_unisim, simprim, ovi_simprim.

-

Altera – altera, ovi_altera, lpm, ovi_lpm, cycloneive , ovi_cycloneive.

ベンダライブラリをプロジェクトに取り込み

コンパイル済みベンダライブラリを取り込むには次の手順が必要となります。

-

Library ManagerのAttach Libraryボタンをクリック

-

編集ボックスに新規ライブラリ名を入力

-

ツールでコンパイル済みライブラリファイル (.lib) を指定

コンパイル済みライブラリは、当社のサポートポータル http://support.aldec.com からダウンロードできます。取り込んだライブラリはLibrary Managerに表示され、追加手順なしで利用出来ます。サポートしているベンダプリミティブは自動認識します。

また、ソースファイルからライブラリをビルドすることもできます。詳細に関しては、“Using ALINT with Aldec and third-party simulators”をご参照ください。

まとめ

ベンダライブラリのネイティブサポートはFPGAデザイン解析の精度を大きく向上させるユニークな方法です。

-

ブラックボックスなし:間違った違反や誤検出を多大に削減。

-

階層の完全把握:チップレベルルールの重大な違反を見落とさない。

XilinxとAlteraの主なライブラリはすでにサポートされていますが、その他のライブラリもご要望に応じてサポートします。support@aldec.com にお問い合わせください。

適用範囲:

-

ALINT 2012 Windows

-

ALINT 2012 Linux

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.