Active-HDLにおけるデザインのシミュレーション方法

概要

本アプリケーションノートでは、Active-HDLシミュレータにおいて、入力信号に値を与えてシミュレーションを実行する方法を説明します。Active-HDLは次のシミュレーション手法や、シミュレーション実行中の入力信号への値の代入をサポートしています。

-

スティミュラスの手動選択

-

TestBench ウィザードから生成されるVHDL/Verilog テストベンチファイル

-

ユーザ作成のVHDL/ Verilog テストベンチファイル

-

VHDL 波形からのテストベンチファイル (IEEE WAVES specification 1029.1準拠)

-

Verilog 結果比較テストベンチファイル

-

コンソールウィンドウから入力されたシミュレーションコマンド

-

シミュレーションマクロコマンドを含むファイル

-

ユーザによる波形エディタをベースとしたシミュレーション入力

上記の全てのファイルや手法を同一デザインに適用することが可能です。特定デザインの要求に最適で、シミュレーションの入力を作成するのに必要となる時間とデザイン検証の複雑さとのバランスがとれるような手法を選択してください。

スティミュレータ

シミュレーションの入力値を作成する最も容易な方法は、波形エディタに必要な信号を追加して、スティミュレータオプションで利用可能な値を割り当てることです。いくつかのオプションが選択可能で、次のタイプをサポートしています。

-

Clock

クロックスティミュレータは、クロック信号をドライブするのに使用します。本タイプは、コマンドforce -repeatを使っても適用可能です。クロックスティミュレータは、次のパラメータで定義される矩形波形を生成します。

-

周波数/周期

-

初期オフセットタイム

-

デューティサイクル

-

初期値

-

-

Counter

カウンタスティミュレータは1次元配列タイプとintegerタイプのVHDL信号およびVerilog integer レジスタとベクタに適用可能で、カウンタの連続値を生成します。カウントステップ、方向、連続カウントの時間間隔、カウンタの初期値、およびカウンタタイプ(バイナリ、グレー、ジョンソン、Circular One, and およびCircular Zero) を設定します。

-

Custom (標準波形のみ)

カスタムスティミュレータは、既存の標準波形上にある信号やネットに値を代入します。波形の編集機能を使って、手動で任意の波形を作成することができます。典型的な使い方は、前回のシミュレーション結果である波形を再利用します。例えばシミュレーション実行中にホットキーを使って特定信号の波形を作成します。連続して実行するシミュレーション時に作成した波形を再利用するために、イニシャライズシミュレーション後にスティミュレータのタイプをホットキーからカスタムに変更します。

-

Formula

式スティミュレータは、定義済みの構文に基づいた記述で任意の波形を生成します。シミュレーション時間とその時の値の連続組み合わせで波形を定義します。さらに式は、指定周期を繰り返し実行するための -repeatオプションを含みむことができます。式の構文は下記の通りです。

<value

-

ホットキースティミュレータは、値スティミュレータと概念が同じですが、強制的に値を変更するのに便利なメカニズムを提供します。値を変更するには、特定キーを押すだけです。通常はキーを押すことにより2つの値、例えば 0 と 1をトグルさせます。ホットキーを連続して切り替えることにより、長い値を定義することもできます。

-

Predefined

定義済みスティミュレータは、クロックまたは式のどちらかをベースとし、独自の名前をつけます。それらの名前によりスティミュレータの参照が可能で、毎回同じ定義を繰り返すことなく、複数の信号に値を容易に代入することができます。

-

Random

ランダムスティミュレータは乱数の生成に基づいていて、標準確率機能により分配されるinteger 値を返します。次の分配機能が利用可能です。

-

Chi-square

-

Erlang

-

Exponential

-

Normal

-

Poisson

-

Random

-

T

-

Uniform

-

-

Value

値スティミュレータは、信号を定数でドライブします。シミュレーションをステップ実行する場合、スティミュレータで再定義することにより、ステップ毎に値を変更することができます。このタイプのスティミュレータは、force コマンドを使うことでも適用可能です。

スティミュレータの利点

-

強制的に信号を必要な状態にする最も速くて簡単な方法

-

スティミュレータのインタラクティブな代入により、シミュレータのレスポンスを即時表示

-

スティミュレータは、全デザイン階層の任意の信号やポートに適用可能

-

下位階層のプロセスやアーキテクチャのデバッグに便利

スティミュレータの欠点

-

VHDL またはVerilog テストベンチは、デザインのトップレベルの信号しかドライブ不可

-

スティミュレータは波形ファイルとして保存

-

スティミュレータはデータファイルを読み込む等の複雑なシミュレーションを実行するには不十分

-

スティミュレータは Active-HDL固有の機能であり、他のHDLシミュレータでは動作不可

波形エディタ

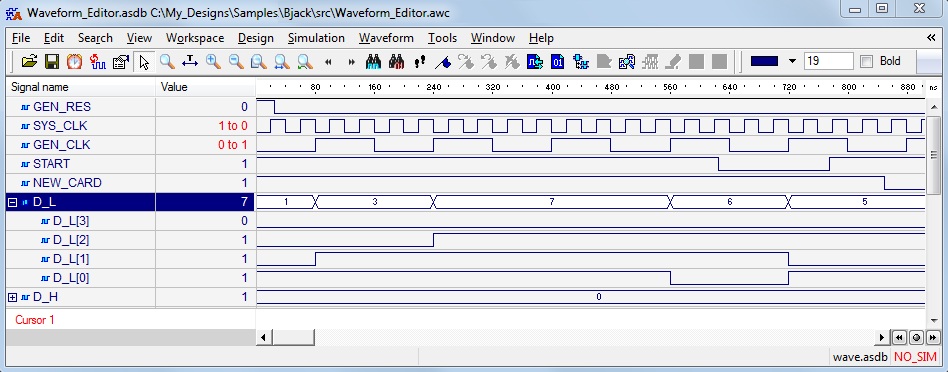

波形エディタを使って、新しい波形上の信号をドラッグ、コピー、ペースト、および描画することにより、波形をグラフィカルに編集することができます。これらの波形は、必要な信号の波形を編集することにより、カスタムスティミュレータとして使用することができます。グラフィカルに編集した波形は、テストベンチウィザードと連携してシミュレーションの入力としても使用することができます。テストベンチウィザードは後述にありますが、編集した波形に基づいてVHDL または Verilog テストプログラムを生成します。

図 1.シミュレーション実行例

シミュレーション結果の比較

波形エディタではシミュレーション結果を比較することができます。違いが検出された信号は、波形ウィンドウに青色で表示されます。Compare Waveformアイコン ![]() を使って波形に表示されている信号値の比較を行います。波形比較の前に、前回のシミュレーション実行結果が保存されていることを確認してください。比較した波形上の信号に違いがない場合には、違いがないことを通知するメッセージが表示されます。

を使って波形に表示されている信号値の比較を行います。波形比較の前に、前回のシミュレーション実行結果が保存されていることを確認してください。比較した波形上の信号に違いがない場合には、違いがないことを通知するメッセージが表示されます。

図 2. シミュレーション実行結果の比較

シミュレーションマクロ

コンソールウィンドウに入力されたマクロ

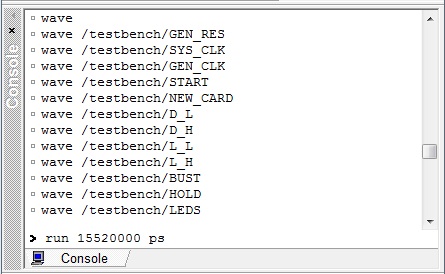

Active-HDLでは、信号値の指定や式の代入、シミュレーションのステップ実行などのシミュレーション用マクロコマンドをコンソールに入力して実行することができます。コンソールウィンドウに適切なマクロコマンドを入力することにより、シミュレーション実行中いつでも、信号に値を代入することができます。マクロコマンドを使って、値を代入した信号を波形に追加することも可能です。

図 3. コンソールウィンドウ

例:

-

Wave - 空の波形ウィンドウを開きます。

-

Wave /testbench/CE - 波形ウィンドウに CE 信号を追加します。

-

Force LOAD 1 0ns, 0 10ns - LOAD 信号に0ns シミュレーション時間に1 を、10ns 経過時に 0 を代入

-

Force CE 1 - CE 信号を1 に変更

マクロを含むファイル

シミュレーションマクロコマンドはファイルから実行可能で、コンソールウィンドウでコマンドを毎回手動で入力する時間を省くことができます。シミュレーションマクロは入力信号に値を代入するだけでなく、他のコマンドを実行することが可能です。これによりデザインの検証処理、特に他のシミュレーションの入力手法を組み合わせた検証を完全に自動化することができます。例えばスクリプトを書いて、複数のテストベンチファイルを使って、次々に多くのシミュレーションを実行することができます。マクロスクリプトにより、論理合成ツールやバッチファイル等の外部プログラムが実行可能です。自動化の目的でActive-HDLに含まれるスクリプト用のカスタムコマンドを呼び出すことも可能です。

マクロコマンドの利点

-

キーボードから直接入力可能な高速シミュレーション

-

GUI ウィンドウの使用が不要

-

ModelSim ユーザが精通

-

シミュレーションの全ての処理のシミュレーションの自動化が可能

マクロコマンドの欠点

-

シミュレーションコマンド特有のフォーマット

-

マクロ言語コマンドの知識が必要

図 4. マクロコマンドファイル

HDL テストベンチ

HDL テストベンチは、シミュレーションの入力を記述したVHDL/Verilog ファイルです。VHDL/Verilogでは、シミュレーション入力を作成するための様々な特有のファンクションや言語構造を使用することができます。テキストファイルからシミュレーションデータを読み込み、入力ポートをドライブする別のプロセスを作成することができます。テストベンチを作成する典型的な方法では、実際のVHDL/Verilog デザインをコンポーネントとして取り扱い、特定の値をそのコンポーネントの入力ポートに代入するような追加のVHDL/Verilog ファイルを作成します。

図 5. テストベンチ

テストベンチモデル

HDL テストベンチでは、シミュレーション入力を与え、デザインの出力をテストすることができます。例えば、デザインの出力をテキストファイルに書き出し、その結果を期待値ファイルと比較するVHDL/Verilogファイルを作成することができます。この手法は、ユーザの手間は最小で、最も確実なデザイン検証方法です。

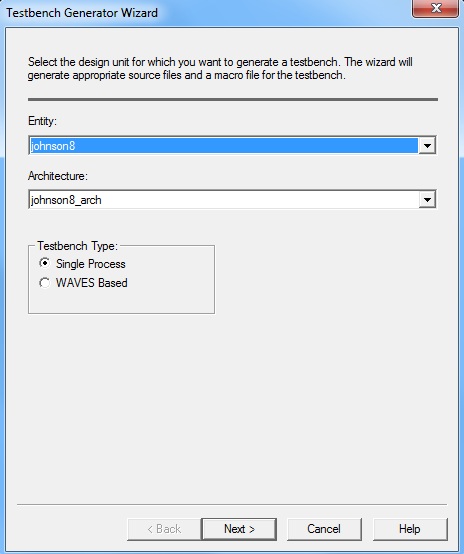

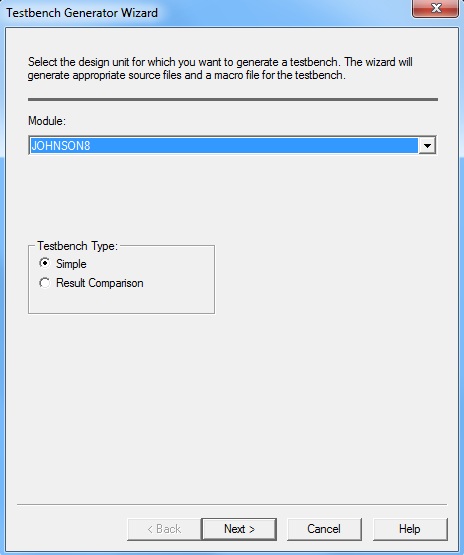

テストベンチウィザードを使ったテストベンチの作成

テストベンチの作成は面倒です。テストベンチウィザードは操作ガイドにより処理を自動化します。まずテスト対象のトップレベルデザインエンティティを選択します。次に必要な入出力ポートを含む波形ファイルの名前を入力します。その他いくつかの質問に答えると、テストベンチウィザードは必要な情報を収集して、テストベンチのテンプレートを作成します。ウィザードが生成したファイルは編集することができ、必要に応じてユーザ独自のテスト項目や入力信号を追加することができます。

図 6. テストベンチウィザード (VHDL)

図 7. テストベンチウィザード (Verilog)

例:

module TOP; reg CLK; reg RES; wire [3:0] Q_UUT, Q_REF, Q_V; reg COMP_RES; integer file; //Component declaration of the tested unit counter1 UUT (.CLK(CLK), .RES(RES), .Q(Q_UUT)); endmodule

IEEE WAVESフォーマットでのVHDL テストベンチ

テストベンチウィザードから、IEEE WAVES 1029.1 仕様に準拠したテンプレートを作成することができます。WAVES はVHDLでテストベンチファイルを作成するための仕様です。VHDLライブラリとして実装されている特定言語でシミュレーションの入力を記述します。いかなる抽象度においてもハードウェアデザインの検証とテストをサポートしています。テストベンチファイルを作成するのに、WAVES仕様に精通している必要はありません。このオプションを選択すると、テストベンチウィザードはWAVES仕様を使って、ユーザのテストベンチを自動フォーマットします。本フォーマットを使用する主な利点は、様々なシミュレータ間で区別なく使用できるよう、シミュレーションの入出力ファイルをフォーマットすることです。WAVES フォーマットは、多くのVHDLコードを記述することなく、シミュレーション出力を比較するための大変有効で高度なファンクションも含んでいます。標準のテストベンチファンクションがコンパイル済のWAVES ライブラリで提供されており、WAVESフォーマットのテストベンチファイルの読み込みおよび書き出しが可能です。

WAVES テストベンチと他のテストベンチファイル間の違い

-

式やスティミュラスタイプを含む波形データの標準ファイルフォーマットを提供

-

典型的なテストベンチ操作に対して大変有効で高度なファンクションを用意

ユーザ作成のHDLテストベンチ

ユーザ作成のVHDL /Verilogテストベンチは、デザインのVHDL/Verilog ファイルの1つとして扱われます。既存のテストベンンチファイルをインポートし、新しい テストベンチを最初から作成することができます。テストベンチファンクションを含むVHDLパッケージをActive-HDL で提供しています。言語アシスタントでは、シミュレーション特有のVHDL/Verilog 構文を使ったサンプルを用意しています。独自のテストベンチの記述に関する詳細情報は、VHDL/Verilog 資料を参照してください。

テストベンチの利点

-

先進的なコードを使って、幅広いシミュレーション入力の記述が可能

-

独自仕様ではないフォーマットにより、どのHDLシミュレータでも同じシミュレーションが実行可能

-

あらゆる設計段階で、シミュレーション入力を与え、デザインの出力を確認することが可能

テストベンチの欠点

-

テストベンチの記述、特に最初のデザイン検証時には時間がかかる

-

テストベンチの記述にはVHDL /Verilog の知識が必要

例:

#Read cycle for rams with memfiles IF (MEMFILE) THEN FOR i IN 0 TO number_of_iterations LOOP a_bus

結論

本ドキュメントで説明したように、Active-HDL はデザインのシミュレーションを実行する様々な手法を提供しています。最善の結果を得るには、各設計段階で最適なスティミュレータを使用します。設計初期に、シミュレーション入力を即座に作成し、デザインのレスポンスを直ぐに表示するには、インタラクティブなスティミュレータを使用します。ユーザデザインのテストプランを考える場合は、スティミュレータからテストベンチウェザードを使ったVHDL/Verilog テストベンチに切り替えます。ユーザが希望するVHDL/Verilog テストファンクションは何でも追加記述することができます。 最後にユーザはバッチモードで、論理合成や配置配線、異なる設計段階での結果の比較などの他のデザインタスクと合わせて、シミュレーションスクリプトを追加し、検証処理を自動化して、テストベンチを呼び出します。シミュレーション入力の作成方法についての詳細情報は、Active-HDLのオンラインドキュメントを参照してください。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.