Active-HDLを初めて利用する方へ

はじめに

このページはActive-HDLの基本機能の使い方を学ぶチュートリアルです。Active-HDLはVHDL, Verilog, System Verilog, EDIF, System Cでデザインを開発し、検証するための統合環境です。このチュートリアルでは、Active-HDLと一緒にインストールされるPressControllerというサンプルデザインを用いて、デザインエントリとシミュレーションを行います。

利用を開始する

チュートリアルを始めるにあたっては、まず、Active-HDLの最新バージョンをコンピュータにインストールする必要があります。http://www.aldec.com/Productsから無料でダウンロードできます。

ワークスペースとデザインを作る

Active-HDLでは、デザインとそのリソース (ソースファイル、シミュレーション結果の出力ファイルなど) はデザインごとにまとめてワークスペースに置いておくことができます。ワークスペースではいくつかのデザインを同時に追加したり処理したりすることができます。

-

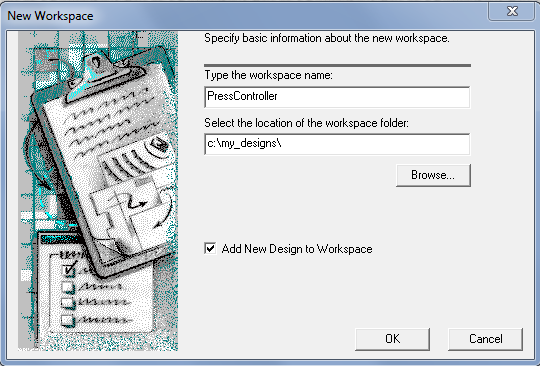

メニューでFile | Newと進み、Workspaceをクリックします。New Workspace Wizardが起動します。

-

ワークスペース名を入力し、プロジェクトを作成したい場所を選びます (Browseボタンでフォルダを探せます)。

注: Create new designオプションにチェックを入れた場合、New Workspace Wizardの後にNew Design Wizardが起動します。この場合新規ワークスペース作成後すぐに (そのワークスペースに格納される) 新規デザインを作成できます。

-

完了したらOKボタンをクリックします (図1参照)。

図1: 新規ワークスペース作成ウィザード (Workspaceウィンドウ)

-

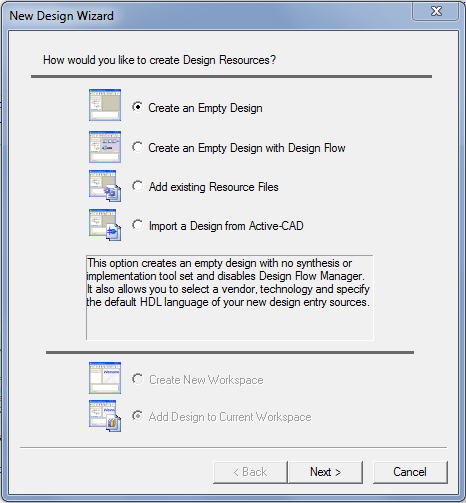

新規デザイン作成のポップアップが表示されます (図2参照)。

図2: 新規ワークスペース作成ウィザード (Designウィンドウ)

-

Design Language、つまりBlock Diagram ConfigurationとDefault HDL Language (今回の例ではVHDL) を選びます。次に必要に応じてVendorとTechnologyからTarget Technologyを選択します。

-

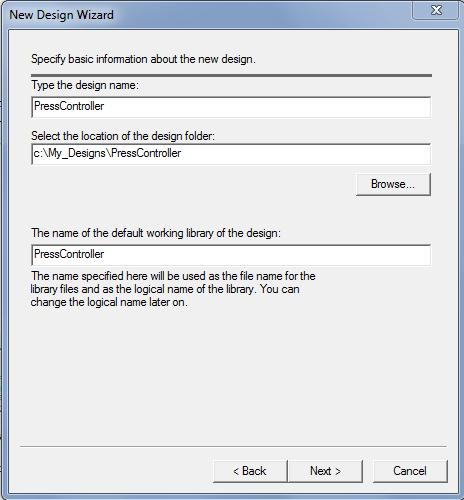

デザイン名を指定し、デザインフォルダの位置 (ワークスペースと同じ) を選びます。デザインのデフォルトのワーキングライブラリの名前はデザイン名と同じです (図3参照)。

図3: New Design Wizard

-

完了したらFINISHボタンをクリックします。

-

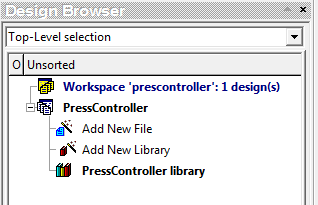

Design Browserにワークスペース名が表示され、そこに新規デザインが格納されます (図4参照)。

図4: ワークスペースとデザイン作成後のDesign Browser

ファイルを作成してデザインに追加

-

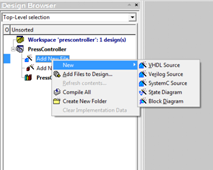

新規ファイルの作成、既存ファイルの追加、ディレクトリの作成などを実行したい場合は、Add New Fileオプションをクリックしてから実行したい作業を選択します。

-

メニューのFile | Newから新規ファイルを開いてデザインディレクトリに保存することもできます (図5参照)。

図5: ワークスペースにファイルを追加

HDLソースコードの作成

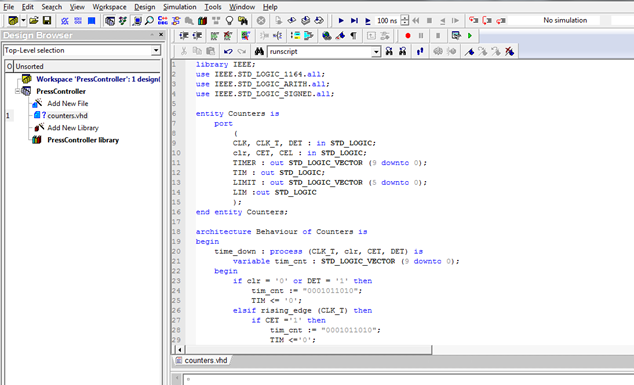

VHDL/Verilog/System Cのソースファイルを作成するには、Add New Fileオプションをダブルクリックしてから、ソースファイルのタイプを選択します。Design Browserの右側に新しいエディタウィンドウが開きます。テキストによるデザインエントリは図6のような形になります。

図6: VHDLソースコードファイルの作成

State Diagram Editorで新規ステートダイアグラムを作成

-

Design BrowserでAdd New Fileをダブルクリックします。State Diagramを選択し、ファイル名を指定します。

-

ポート、信号、ステートおよび遷移が追加可能です。FSMメニューのヘルプが参照可能です。

ポートをダイアグラムに追加

-

FSMメニューからPort | Input/Output/Bidirectional Portを選択します。

-

マウスカーソルをダイアグラムシート (マシンフレームの上) の上に移動し、ポートを置きたい場所をクリックします。

-

ポートにはデフォルト名が与えられます。名前を変更するには、ポート記号を右クリックし、ショートカットメニューからPropertiesを選択します。次に、Port Propertiesダイアログで名前を変更し、OKをクリックします。

ダイアグラムに信号や変数を追加

-

FSMメニューからSignal/Variableを選択します。

-

変数を定義するには、マウスカーソルをマシンフレーム内に移動し、信号・変数記号を置きたい場所をクリックします。

-

内部信号を定義するには、マウスカーソルをダイアグラムシート (マシンフレームの上) の上に移動し、信号・変数記号を置きたい場所をクリックします。

-

変数・信号にはデフォルト名が与えられます。名前を変更するには、記号を右クリックし、ショートカットメニューからPropertiesを選択します。次に、Propertiesダイアログで名前を変更し、OKをクリックします。

ダイアグラムにステートを追加

-

FSMメニューからStateを選択します。マウスカーソルが新しい形になります。

-

マウスカーソルをマシンフレーム内に移動し、ステートを置きたい場所をクリックします。

-

ステートにはデフォルト名が与えられます。名前を変更するには、記号を右クリックし、ショートカットメニューからPropertiesを選択します。次に、State Propertiesダイアログで名前を変更し、OKをクリックします。

-

ステートアクションを割り当てるには、FSMメニューからAction | Stateを選択します。マウスカーソルの点をステート内部に移動し、クリックして固定します。編集ボックスが表示されますので、アクション文を入力してから、ダイアグラムの別の場所をクリックして編集ボックスを閉じます。

-

エントリーアクションを割り当てるには、FSMメニューからAction | Entryを選択します。マウスカーソルの点をステート内部に移動し、クリックして固定します。編集ボックスが表示されますので、アクション文を入力してから、ダイアグラムの別の場所をクリックして編集ボックスを閉じます。

ステート間遷移を描く

-

FSMメニューからTransitionを選択します。マウスカーソルが新しい形になります。

-

遷移の開始点とするステートの内部をクリックします。

-

遷移の終点とするステートの内部をクリックします。遷移の線が表示され、マウスカーソルの形は通常の選択カーソルに戻ります。

-

遷移の矢印の形を変えるには、矢印に付いている長方形のマーカーまたは矢印の真ん中の部分をドラッグします。

-

ダイアグラム内の別の場所をクリックすると遷移の矢印の選択状態が解除されます。マーカーは消えます。

-

遷移の条件を指定するにはFSMメニューからConditionを選択します。

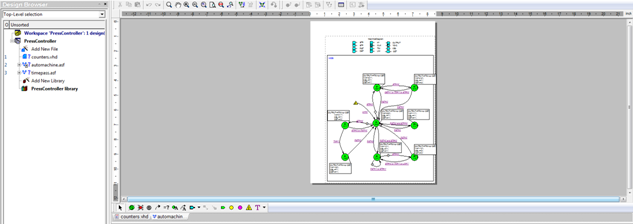

今まで説明したものをすべて追加すると、ステートダイアグラムは図7のようになります。

図7: ステートダイアグラム

Block Diagram Editorで新規ブロックダイアグラムを作成

-

Design BrowserでAdd New Fileをダブルクリックします。Block Diagramを選び、ファイル名を指定します。

-

BDEメニューのヘルプを参照しながら、シンボル、ワイヤ、バス、FUB (関数ユニットブロック)、HDL文を追加していきます。

ブロックダイアグラムにシンボルを追加

-

ViewメニューからSymbol Toolboxを開きます。Symbol Toolboxからシンボルをドラッグしてダイアグラム内に配置します。

-

Symbol Toolboxウィンドウ上で右マウスボタンをクリックし、ショートカットメニューからLibrariesを選びます。Symbol Toolboxウィンドウの中身がアップデートされます。

新規ワイヤを追加

ワイヤを描く方法は2つあります。1つは2回クリック、もう1つはマウスボタンを押し続けながら描く方法です。

-

DiagramメニューからWireをクリックします。

-

ワイヤの始点にしたい場所をクリックします。

-

ワイヤの終点にしたい場所までマウスカーソルを動かします。マウスカーソルを動かしている間、始点からカーソルの位置までワイヤの線が伸びていきます。ワイヤを曲げたい場合は、その位置でマウスボタンをクリックします。

-

ワイヤの終点にしたい位置でクリックします。ダイアグラム内の何もない場所でワイヤを切りたい場合は、シングルクリックでなくダブルクリックする必要があります。

-

別のワイヤを描くにはステップ2から4を繰り返します。

マウスボタンを押し続ける方法でワイヤを描く方法は次の通りです。

-

Diagramメニューから、Wireをクリックします。

-

ワイヤの始点にしたい位置にマウスカーソルを動かし、マウスボタンを押します。

-

マウスボタンを押し続けながら、マウスカーソルをワイヤの終点にしたい位置まで動かします。始点からカーソルの位置までワイヤの線が伸びていきます。ワイヤを曲げたい場合は、その位置でマウスボタンを押したままSpaceキーを押します。

-

終点にしたい位置でマウスボタンを放します。

-

別のワイヤを描くにはステップ2から4を繰り返します。

バスの追加

新規バスの描画方法はワイヤと同じです。DiagramメニューでWireの代わりにBusを選び、その後は新規ワイヤを追加のステップ2〜4を繰り返します。

FUBを追加

新規FUB (関数ユニットブロック) の描画方法はワイヤと同じです。DiagramメニューでWireの代わりにFUBを選び、その後はワイヤのステップ2から4までを実行します。

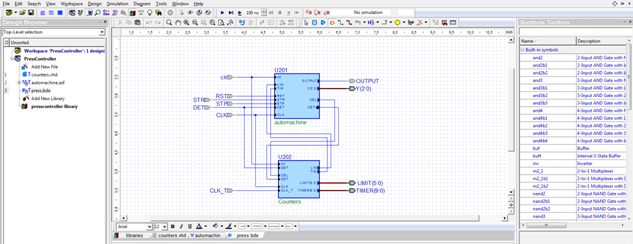

すべてを追加し終えたところで、ブロックダイアグラムは図8のようになっています。

図8: ブロックダイアグラム

テストベンチを生成

Testbench Wizardはユーザー定義要件に基づいてテストベンチファイル (マクロファイル1つとソースファイル多数から構成) を自動生成します。ユーザーの指定する情報でもっとも重要なのは、テストベクタファイル名です。テストベンチはそのファイルに定義されたテストベクタをベースにしてUUTエンティティに対してスティミュラスを生成します。

Testbench Wizardは次のファイルタイプを扱えます。

-

Standard Waveform Viewer/Editorファイル (*awf) またはAccelerated Waveform Viewerファイル (*.asdb)

-

WAVES互換のテストベクタファイル (*.vec)

-

所定の波形を発生させるコードの記述されたVHDL/Verilogソースファイル (*.vhs, *.ver, *.vhr)

テストベンチの生成方法

-

ToolsメニューからGenerate Testbenchを選択します。

-

またはDesign BrowserのFileタブから、デフォルトのワーキングライブラリまたはソースファイル (HDLファイル、ブロックダイアグラムファイルまたはステートダイアグラムファイル) を表示するツリーを展開します。テストベンチを生成させたいエンティティとアーキテクチャのペアか、モジュールまたはセルを右クリックし、ショートカットメニューからGenerate Testbenchを選択します。

コンパイル

コンパイルとはソースファイルを解析する工程です。ファイル内にあるデザインユニットが解析され、シミュレータに理解できるフォーマットでワーキングライブラリに保存されます。Active-HDLでは、ソースファイルはVHDLファイル、Verilogファイル、EDIFネットリストファイル、ステートダイアグラムファイル、およびブロックダイアグラムファイルです。

ブロックダイアグラムファイルまたはステートダイアグラムファイルの場合、コンパイラはダイアグラムから生成されたHDLコード (またはネットリスト) を持つVHDL/Verilog/EDIFの中間ファイルを解析します ($dsn\compile)。Active-HDLはVHDL, Verilog, EDIF用に別々のコンパイラを用意しています。メニューコマンドやツールバーボタンからコンパイルを選択すると、Active-HDLは自動的にコンパイル対象のソースファイルのフォーマットに適合したコンパイラを選び出します。

ファイルのコンパイル

-

ファイルを1つコンパイルする場合は、Design BrowserのFileタブを開き、ファイルを右クリックしてショートカットメニューからCompileを選びます。

-

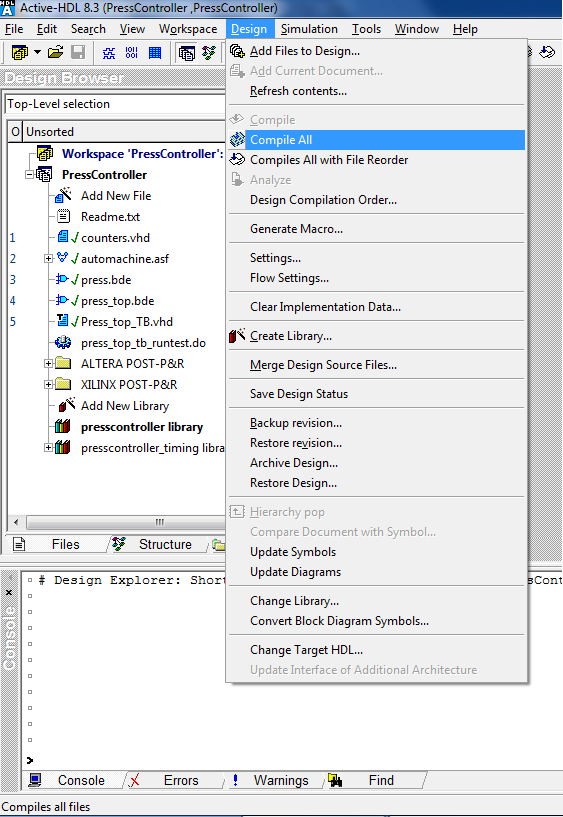

特定のデザインに対してDesignメニューからCompile Allを選択すると、コンパイラは自動でソースファイルを整理してデザインユニットを正しい順序でコンパイルします (図9参照)。

図9: ファイルのコンパイル

-

VHDLファイル (VHDLにターゲットされたブロックダイアグラムファイルとステートダイアグラムファイルを含む) だけが整理されます。それ以外のソースファイル (VerilogとEDIF) は無視されます。

注:

-

コンパイル中に出されたメッセージ (情報、警告、エラー) はConsoleウィンドウか、(指定した場合には) Compilationタブに表示されます。

-

ソースファイルのコンパイルで生成されたライブラリユニットはソースファイル用に指定されたワーキングライブラリに格納されます。デフォルトでは、デザインのソースファイルはすべてデフォルトのワーキングライブラリにコンパイルされます。

シミュレーションの初期化

必要なデザインユニットのコンパイルがすべて成功したら、シミュレーションの初期化が可能になります。シミュレーションの初期化の前に、次を確認してください。

-

トップレベルのデザインユニットを選びます。トップレベルの選択方法は3つあります。

-

Design Browserウィンドウ最上部のドロップダウンリストからVHDLデザインエンティティまたはコンフィグレーション、Verilogモジュール、EDIFセル、またはSystemCモジュールを選択します。

-

Filesタブでソースファイルのストラクチャ (トップレベルユニットを含む) または現在のワーキングライブラリを展開し、デザインユニットを右クリックし、ショートカットメニューからSet as Top-Levelを選択します。

-

Design Settingウィンドウを開きます。デフォルトではGeneralカテゴリーが表示されます。Top-levelカテゴリーを開き、デザインユニットリストからトップレベルユニットを選択します。

-

-

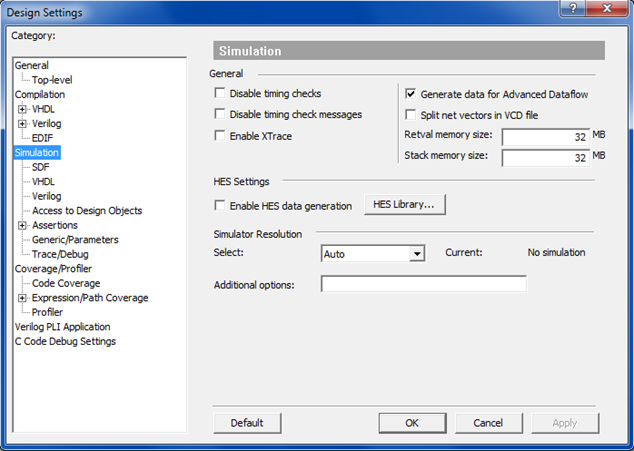

シミュレーション精度 (Simulation Resolution) の値を設定します。それには、DesignメニューからSettingsを開きます。Design Settingsダイアログボックスが開くので、Simulationカテゴリーで、シミュレーション精度の値を指定するか、Autoを選択します。OKをクリックしてダイアログを閉じ、操作を完了します (図10参照)。

図10: シミュレーション精度の設定

トップレベルユニットを選択せずにシミュレーションを実行すると、Active-HDLはすぐに選択するよう促すダイアログボックスを表示します。

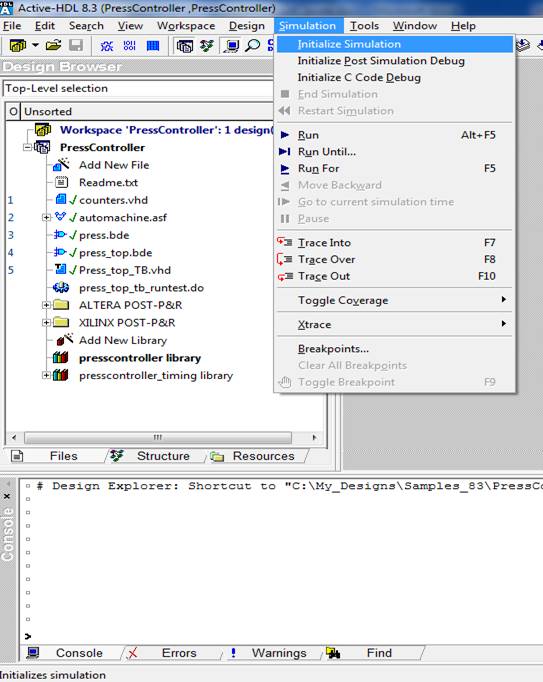

シミュレーションを開始するには、SimulationメニューからInitialize Simulationを選択します。選択すると、シミュレーションモデルのエラボレーションと初期化が始まります。エラボレーションでは、シミュレータはデザインユニットを読み込んでシミュレーションモデルをコンピュータのメモリ上に構築します。初期化では、モデルのオブジェクト (信号、変数など) すべてに初期値 (デフォルト値または明示的に指定した値) が与えられ、同時並行処理がすべて停止まで実行されます (図11参照)。

図11: シミュレーションの初期化

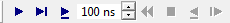

時間を指定せずにシミュレーションを実行するには、SimulationメニューからRunを選びます。所定のタイムステップの間だけシミュレーションを進めたい場合は、メインツールバーのSimulation Stepボックスに所定のタイムステップを入力します (図12参照)。SimulationメニューからRun Forを選択するか、Run Untilを選択します。シミュレーションを実行したい時間を指定し、OKをクリックします。

図12: Simulation Stepボックス

シミュレーションの一時停止と終了

-

その時のシミュレーション時間でシミュレーションを一時停止するには、SimulationメニューからPauseオプションを選択します。

-

シミュレーションセッションを終了するには、SimulationメニューからEnd Simulationを選択します。

-

シミュレーションを再開するには、SimulationメニューからRestart Simulationを選択します。

波形ビューア

Active-HDLには2種類の波形ビューアがあります。:

-

Accelerated Waveform Viewer: バイナリのシミュレーションデータベース (*.asdb) として保存されているシミュレーションデータを表示します。

-

Standard Waveform Viewer/Editor: *.awfのテキストファイルで保存されているシミュレーション結果を表示します。

デフォルトではAccelerated Waveform Viewerが有効で、*.asdbシミュレーションデータベースがシミュレーション初期化中に作成されます。Accelerated Waveform Viewerはデザインで大規模なシミュレーションデータを扱う場合に適しています。このビューアは大規模デザインと長時間のシミュレーション実行に最適化されています。

Standard Waveform Viewer/Editorは小規模なデザインを、特に対話的モードで扱いたい場合に適しています。例えば、このビューアは現在のシミュレーションが前回のシミュレーション結果をどう上書きするか表示できるだけでなく、ホットキーシミュレータを使うこともできます。

新規波形ファイルを開き信号を追加

-

新しい波形ウィンドウを開くには、FileメニューでNew | Waveformを選択するか、ツールバーでNew Waveformをクリックします。

-

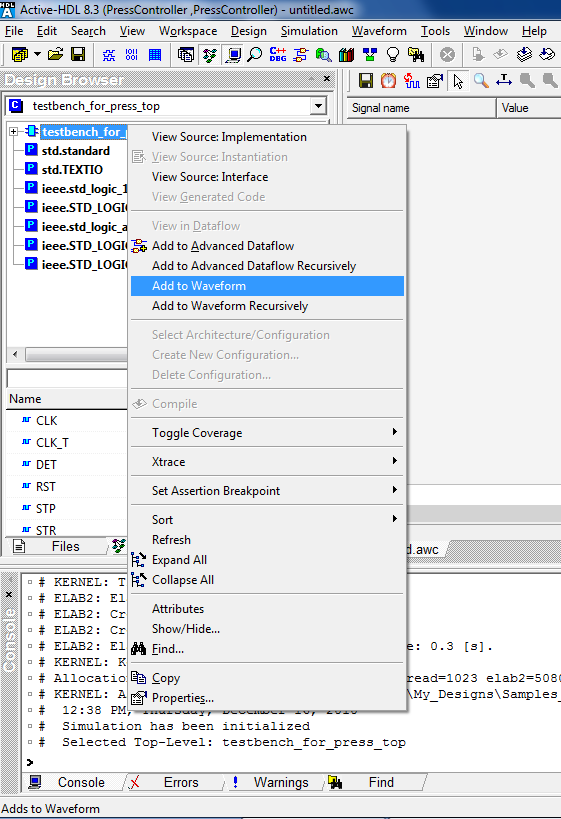

シミュレーションを開始する前に、テスト対象モデルまたは内部信号の入力ポートと出力ポートを表す信号を選択する必要があります。波形ファイルに信号を追加するには、Design BrowserからStructureタブを開き、トップレベルのデザインファイルをクリックします。トップレベルデザインを右クリックして、Add to Waveformオプションを選択します。これは1個以上のオブジェクトを波形ウィンドウに追加するオプション (Design Browserでの表示順序、選択順序、または手動でオブジェクトを選択した通りの順序で、信号が追加されます) です。選択した階層から、その下にある領域を含めて、すべての信号を追加したい場合は、StructureタブのコンテキストメニューにあるAdd to Waveform Recursivelyを選択します。また、Structureタブの上部領域または下部領域からオブジェクトを波形ウィンドウにドラッグして追加することもできます (図13参照)。

図13: 信号を波形ビューアに追加

波形ファイルを保存してオフラインで表示

-

シミュレーションが完了するか、指定した時間実行されたら、File | Saveメニューで波形を保存できます。

-

保存した.awcファイルはオフラインで確認できます。

注: シミュレーションを停止してから波形ファイルを保存してください。

リスタートボタンをクリックすれば波形の信号を消すことなくシミュレーションを再初期化できます。

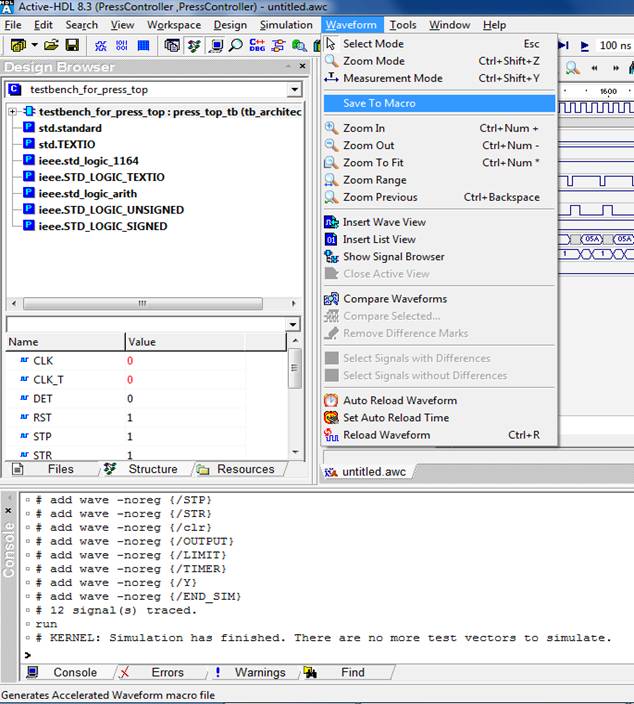

後のシミュレーションで再利用するために波形ファイルを保存

The Waveform | Save to macroメニューオプション、またはFile | Exportメニューは、後のシミュレーションで波形ビューアの表示を復活させられるマクロファイル (.do) を生成するコマンドです。マクロファイルには*.asdbファイルにあるすべての信号についてadd waveコマンドやlistコマンドが記述されています (図14)。

図14 : マクロに保存

マクロファイルを実行

保存したマクロファイルを利用することで別のシミュレーション実行時に信号を波形に追加できます。シミュレーションを初期化した直後に、スクリプトでマクロファイルを実行します。

ヘルプ

ツール内

Help | Product HelpでActive-HDLのヘルプを開き、ツールについて色々学びましょう。

ウェブサイトのヘルプ

www.aldec.com/supportから、Active-HDLに関するオンラインデータベースや技術ドキュメントにアクセスできます。

サポートアカウント

www.aldec.com/supportからアルデックのサポートアカウントに登録すれば、サポート事例を開いたりソフトウェアをダウンロードしたりすることができます。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.