協調エミュレーション

協調エミュレーションとは、エミュレートされるデザインとその周辺機器を接続して、実際の動作環境を再現することです。色々な環境内で応用可能で、目的も色々考えられます。

- 仮想プラットフォームとの接続 – システム全体の検証

- 仮想ペリフェラルとの接続 – 動作環境をモデリング

- インサーキット・エミュレーション – 実際の動作環境内でテスト

- ソフトウェア・デバッガとの接続 – ファームウェアの開発・検証

環境と目的は自由に組み合わせができます。

仮想プラットフォーム

SoCの時代においては、仮想プラットフォーム(VP)は、初めにシステムアーキテクチャの検討に、次いでSoC検証用としてゴールデンなリファレンスモデルとして、広く使われるようになりました。またファームウェアとソフトウェアの開発でも、仮想リファレンスモデルはSoCプロトタイピングよりも早い時期に使えるので、VPが非常に重宝することが分かってきました。

VPを利用した協調エミュレーションは設計開発・検証チームにとって色々なメリットがあります。

仮想プラットフォームを利用した協調エミュレーションの利点

- エミュレータは仮想モデル(カスタムペリフェラルなど)がない場合の代替になる

- VPはRTLコードで使えないモジュール(ARM® Cortexなどのライセンスの必要なプロセッサなど)の代替になる

- エミュレーションは実ハードウェア精度を保証

- エミュレータは複雑な仮想モデルより高速

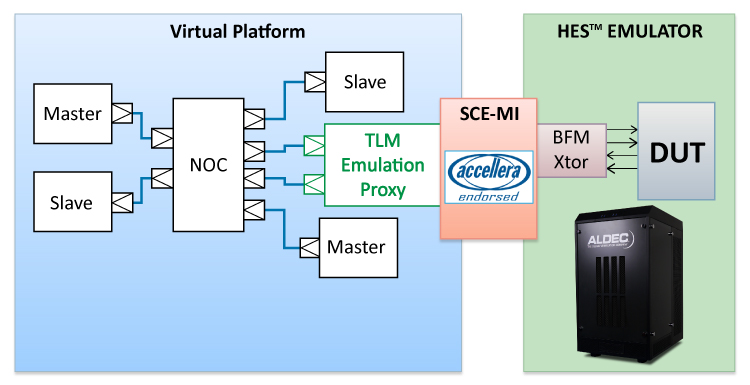

仮想プラットフォームはSystemCシミュレーション・カーネルをベースにしていることが多く、TLMをインタフェースとしてシミュレーション・モデルを接続します。エミュレートされるデザインも同じインタフェースで接続可能です。

アルデックのHES-DVMの用意したAccellera SCE-MI規格の実装は、速度が最適化された形で、仮想プラットフォームとエミュレータの間でメッセージを送受信するチャンネルとして使用されます。SCE-MI C/C++ APIは簡単にTLMプロキシ・モジュール内にラッピングすることが可能で、どのようなSystemC/TLM仮想プラットフォームにもシームレスに組み込むことができます。SCE-MIは無時間モデル(untimed model)、低精度時間モデル(loosely timed model)など、色々なタイミング精度のインプリメントに向いています。アルデックのHES™はARM® Fast Models, Imperas OVP、EDAメーカー製のものなど、サードパーティの仮想プラットフォームとの共存にも成功しています。

実証済みの検証用IPが使えるかどうかも、デザインの検証を成功させるために重要です。エミュレータを仮想プラットフォームに接続するには、所定のバスインタフェースのバス・ファンクショナル・モデルのトランザクタ(BFM Xtor)とTLMエミュレーション・プロキシ・モジュールを仮想プラットフォーム内部でインスタンス化する必要があります。現在、アルデックはAMBA AHB, AXI, OCPバス用TLM 2.0プロキシ・ラッパーを持つトランザクタを用意しています。

メリット:

- VP+エミュレータのハイブリッド環境は速度と精度を犠牲にせずにSoC全体の検証が可能

- 高速FPGAベースのエミュレーションと仮想プラットフォームをシームレスに統合

- AccelleraのSCE-MIで再利用と生産性向上

- 標準的なSystemC/TLMインタフェースと幅広いタイミング精度をサポート

- AMBA AHB, AXI, OCPインタフェースを標準サポート

- エミュレートされるモジュールはRTL精度だがVPに十分な速度

- エミュレーション自動設定

仮想ペリフェラル

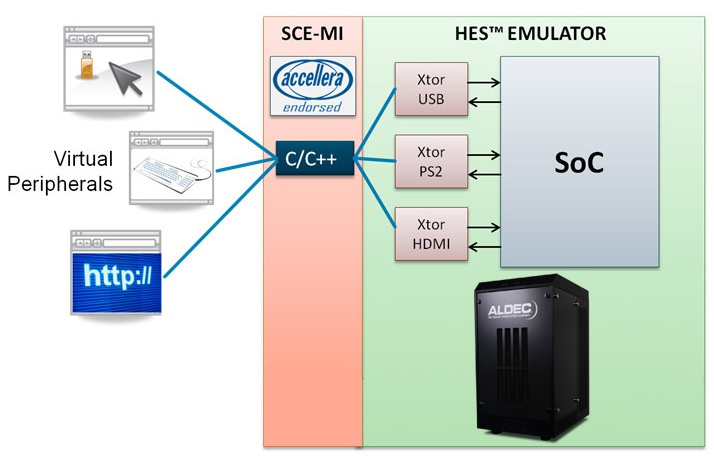

システム・オン・チップ(SoC)はより多くの機能を1個のダイに収めるようになっているとはいえ、ディスプレイ、キーボード、センサ、マルチメディアポートなどの外部ペリフェラルとの接続はやはり必要です。そのため、ペリフェラルのモデルが全部揃っていて初めてSoC検証環境が完成します。やり方の1つとしてあるのが仮想ペリフェラルで、これはエミュレーション・ホスト上またはリモートで実行されるアプリケーションで、トランザクタを介してエミュレートされたデザインに接続します。

アルデックのHES-DVMは速度の最適化を適用したAccellera SCE-MI規格を実装しています。これは再利用可能なトランザクタと仮想モデルの開発に最適なフレームワークです。

また、USB, ギガビットEthernet, HDMI, VGA, PCIe, JTAG, UART, I2Cなどのインタフェース用に、そのまま使えるトランザクタも用意しています。仮想ペリフェラルの開発と組込がすぐにできるように使いやすいAPIも用意されています。詳しくは、検証用IPのページをご覧ください。

メリット:

- SCE-MIに基づく再利用可能な仮想ペリフェラルの実装

- ユーザ・インタフェースを含む完全なSoC検証環境

- 容易なメンテナンスと再構成可能な検証環境

- 最も一般的に使用される即時利用可能なトランザクタ

- インサーキット・エミュレーション への厳しい要求の代替

インサーキット・エミュレーション

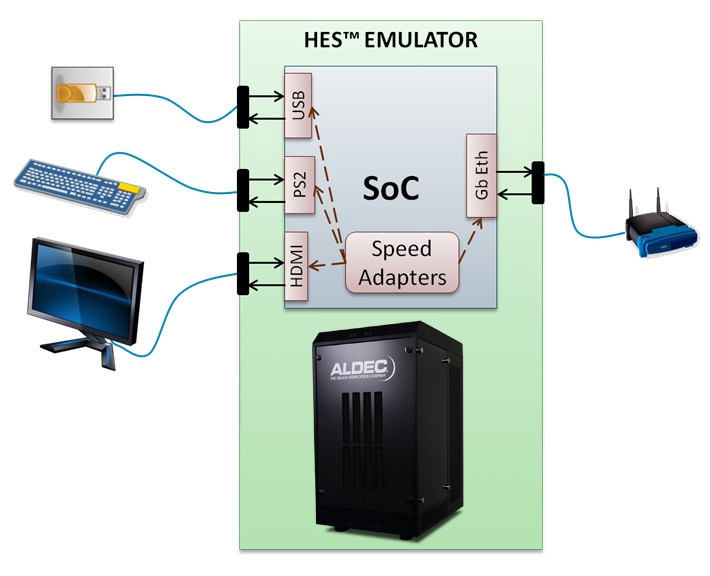

ICEはエミュレーションデザインの検証手法として昔からある方法で、実デバイスを外部ペリフェラルを介してエミュレータに接続します。

FPGAプロトタイピング・ボードで構成されたエミュレータは、さまざまなコネクタを多数並べた専用のエミュレータに比べても大きく有利です。さらに、こうしたコネクタはボードに複数搭載されたFPGAのそれぞれに対応付けられるので、外部デバイスの接続とデザインのパーティショニングも簡単です。FPGAプロトタイピング・ボードのコネクタがオープン仕様であれば、PHYデバイスを搭載した専用のドーターカードを開発して接続するのも非常に簡単です。HES-7と社内開発のボードの多くにそれが当てはまります。

ICEでは、外部デバイスも、エミュレートされるクロックよりも高速なターゲットのスピードでの動作を要求されることも非常に多くあります。スピードアダプタ・モジュールを適用するのはこのようなケースです。スピードアダプタは特殊な検証用IPとして扱われ、実クロックドメインをエミュレートされるクロックから分離し、データ転送のバッファを設けます。

スピードアダプタはエミュレータのメーカーから入手することもできますが、社内開発もできます。アルデックはペリフェラルをフルスピードで確実に接続できるように、標準的なインタフェース用のスピードアダプタを提供しています。

メリット:

- ICEでは実データストリームでのテストが可能

- FPGAプロトタイピング・ボードとの接続方法多数

- エミュレーション用・プロトタイピング用にペリフェラルのドーターカードを開発可

- 既製のスピードアダプタを提供可能

インターゲット・ファームウェア検証

SoCでソフトウェアとファームウェアの検証が必要な場合、協調エミュレーション技術が欠かせません。仮想プラットフォームの高抽象度仮想モデルは精度が足りないことが非常に多いですが、RTLシミュレーションの方は速度が桁違いに遅すぎます。ソフトウェア検証、能率的なデバッグ、SoCの完成において、協調エミュレーションが鍵になっています。

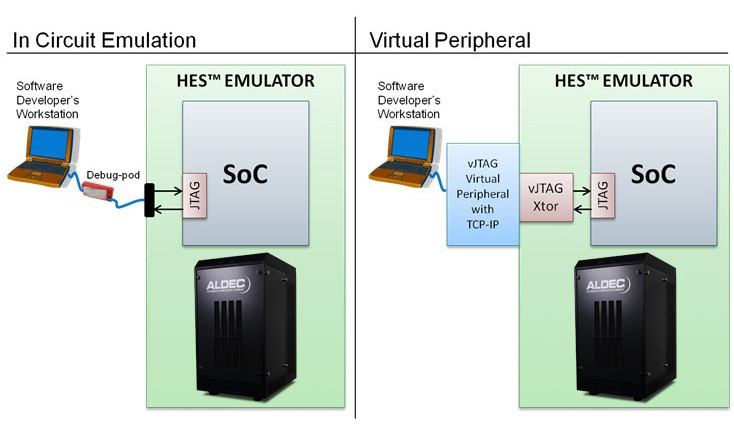

ソフトウェア開発者が使うソフトウェア・デバッガは、組込プロセッサと色々な方法でインタフェースを取ります。例えば、特別なデバッギング・ポートや標準的なJTAGなどが使われます。どんな方法を使うにせよ、インサーキット・エミュレーション(ICE)と仮想ペリフェラルという、2つの協調エミュレーション技法のどちらかを適用できます。

ICEの場合、JTAGやデバッギング・ポートはオンボード・コネクタから引き込み、デバッグ用デバイスを接続できます。これは適当な接続方法があれば実現できる従来的な方法で、FPGAプロトタイピング・ボードでよく利用されます。マイクロプロセッサでエミュレートされたJTAGコントローラとインタフェースするのは、スピードアダプタなしで直結できるReactive TCK(RTCK)ポートがある場合特に簡単です。言うまでもありませんが、ICEベースのソフトウェア・デバッガはアルデックのHES™でサポートされています。

仮想ペリフェラルの技法はこれよりもずっと柔軟な対応が可能です。アルデックの仮想JTAG(vJTAG)トランザクタとTCP/IPをサポートする仮想ペリフェラルを使えば、LAN経由でソフトウェア・デバッガを接続できます。ラボのエミュレータ上で走るソフトウェアをデバッグする時でも、開発者はワークステーションのある自分の席に座ったままでできます。デバッグ用デバイスを用意する必要もないので、プラットフォームの保守も楽で、拡張性も確保できます。

仮想ペリフェラルには、ARM® VSTREAMもあり、これもHES™でサポートされています。

メリット:

- ターゲット・ハードウェアでシリコン製造前ファームウェア検証

- ハードウェア・ソフトウェア協調検証

- ICEか仮想ペリフェラルかを選択可

- 実績あるvJTAGトランザクタを提供

- TCP/IP機能を持つvJTAG仮想ペリフェラルでネットワークアクセス可能

- vJTAGでスケーラブルな検証プラットフォーム

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.