UVMシミュレーション・アクセラレーション

大規模化し続けるASICデザインの検証において、HDLシミュレーションの速度が主要なボトルネックとなっています。タイトなスケジュールに合わせるためにシミュレーション・テストの数を抑えるのは逆に危険で、検証が完璧に終わるかどうか疑問です。

UVMやVMMのような新しい手法は制約付きランダム生成で検証プロセスを自動化しますが、必要なシミュレーション時間がさらに延びてしまいます。

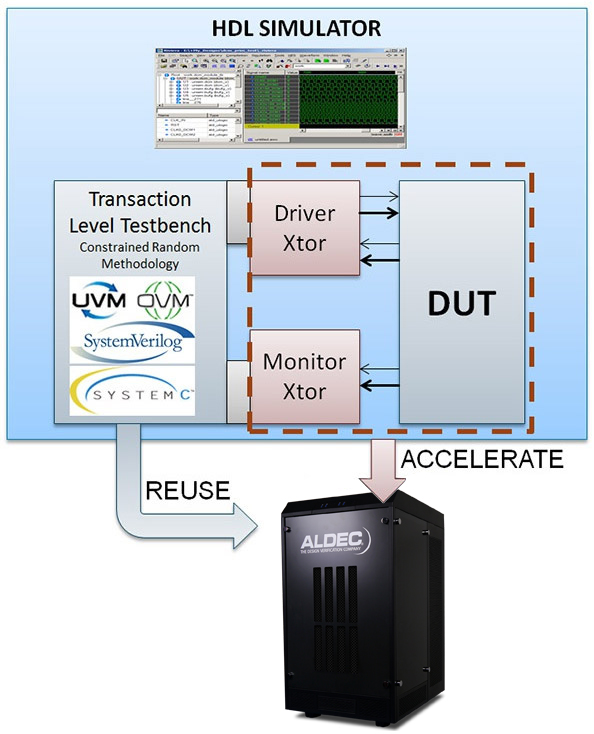

長期化が続くシミュレーション時間に対する対策は、シミュレーションの高速化にエミュレーションの技法を応用することです。

シミュレーションを高速化するには、リソースを多く占めるモジュールをFPGAボード上に配置しつつ、シミュレーションの制御はHDLシミュレータで行うようにします。この検証手法はHDLシミュレーションの利点(信号の可視性)とエミュレーションの利点(スピード)を両立させるものです。さらに、この高速化技法ではシミュレーション・テストベンチを機能性や検証手法を損なうことなく再利用します。

HES-DVM™では、数100万ゲートレベルのSoCデザインのシミュレーションの場合、HDLシミュレーションだけの場合に比べて1000倍以上の高速化が可能です。考えられるすべての検証環境は次の2段階の信号抽象化レベルでカバーされます。

トランザクション・レベル・アクセラレーション

最近の傾向では、検証環境の抽象レベルを信号レベルからトランザクション・レベルに上げるようになっています。この変化によるメリットは次の通りです。

- テスト環境の再利用

- 制約付きランダム・シナリオによるテストベンチ強化

- デザインの問題点の追跡とデバッグの促進

- 検証の高速化

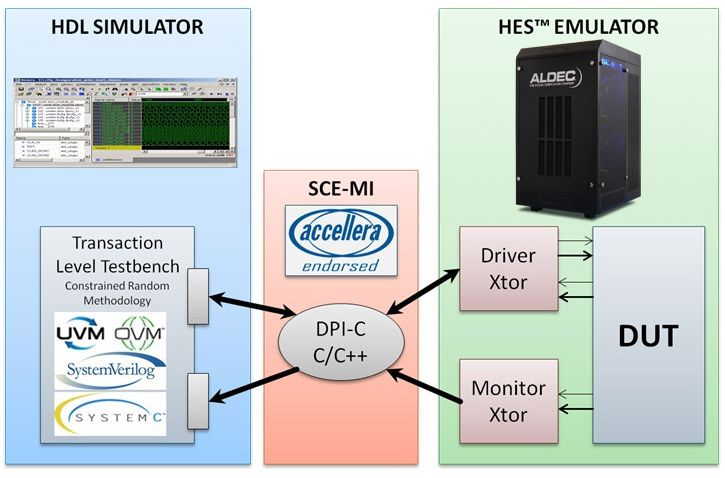

HES-DVMはこのトレンドと歩調を合わせ、トランザクション・レベルのテストベンチでエミュレーション技術によるシミュレーション・アクセラレーションを応用できるようにしています。トランザクション・レベルのシミュレーション・アクセラレーションの基礎はAccelleraのStandard Co-Emulation Modeling Interface (SCE-MI) 規格です。

HES-DVMのDesign Verification Manager (DVM) はSCE-MIのFunctionとMacro Basedの両バージョンをサポートし、トランザクタ(Xtors) を持つDUTを自動コンパイルし、HES-7™などのFPGAプロトタイピング・ボードや社内開発のボードでエミュレーションができるようにします。テストベンチは全体が再利用可能なので、エミュレータでシミュレーション・アクセラレーションが実現できます。

トランザクタ・レベル・テストベンチで動作するエミュレーションはHDLシミュレーションだけの場合と比べて1000倍以上も高速で、制約付きランダムを用いた検証手法は効率が落ちるという問題の克服に成功しました。

HES-DVMの網羅的デバッギング機能を活用することで、デザイン・ブロックがSoCへの組込ができない状態でもシミュレーション・アクセラレーションが適用できます。

メリット:

- 高倍率の高速化

- シミュレーション・テストベンチと環境を再利用

- どんな種類のテストベンチにも対応

- サイクルベース精度と信号レベル精度

- HDLシミュレータとシームレスに統合

- 網羅的なデバッギング・オプション

- デザインの自動セットアップ

信号レベル・アクセラレーション

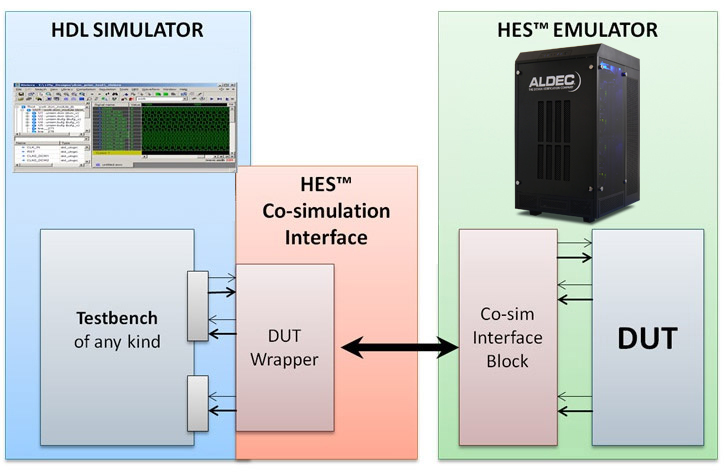

信号レベル・アクセラレーション・モードは非常に柔軟性が高く、システム全体の高速化も、低階層レベルの一部ブロックだけの高速化にも対応しています。テストベンチの種類や検証手法に関して何の前提も要りません。シミュレータのテストデザイン(Design Under Test, DUT)はVHDL, VerilogまたはSystemCのラッパーで代替しますが、これは元のモジュールと信号レベルで互換性があります。DUTはエミュレータ上で実行されるので、HDLシミュレータの負荷を大部分削減できます。

アルデックはPLI/VHPI規格と互換性を持つHES™協調エミュレーション・プラグインライブラリを提供しています。シミュレーション・アクセラレーションはアルデックのツールにも、サードパーティのHDLシミュレータにも適用できます。

デザインのコンパイルとセットアップ、DUTラッパーの生成などはすべてHES-DVMのDesign Verification Manager (DVM) が自動で行います。

HDLデザインはFPGAボードで高速化されますが、メインのデバッギングツールは引き続きHDLシミュレータが使えます。これは、デザインの出力信号とデバッグプローブはすべてシミュレータの波形ビューワにフィードバックされるためです。そのため、デザインサイクルの早い段階でもシリコンレベルの精度でデザインをデバッグし、高速なシミュレーションを実行できますので、今までに比べて非常に短い時間でバグやエラーをより多く発見することができます。

メリット:

- 高倍率の高速化

- シミュレーション・テストベンチと環境を再利用

- どんな種類のテストベンチにも対応

- サイクルベース精度と信号レベル精度

- HDLシミュレータとシームレスに統合

- 網羅的なデバッギング・オプション

- デザインの自動セットアップ

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.