リンティング/デザイン解析

スタティックリンティング

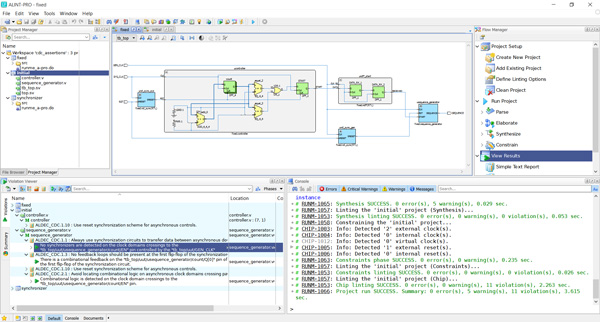

アルデックのALINT-PRO™は、RTLレベルのFPGAおよびASICデザイン向けの高度なデザインルールチェック(DRC)ソリューションで、いまいちなコーディングスタイル、 不適切なクロックおよびリセット管理、不適切に同期されたクロックとリセットドメインクロッシング(CDC、RDC)、シミュレーションと合成結果の不一致、誤って実装された有限ステートマシン(FSM)、不十分なテスト容易性、設計フロー全体のその他の一般的なソースコードの問題など、さまざまなデザインの問題の検出に役立ちます。アルデックのALINT-PROは、設計入力段階で設計者自身の生産性ツール(HDLエディタのバックグラウンドでRTLコードの単体ユニット内の問題をリントおよびデバッグすることにより)、またフルデザイン階層で完全なリンティング(正式なコードレビュー、マイルストーンサインオフ、レグレッションテストフロー、継続的統合環境)を実行する企業検証フローの一部として利用することが出来ます。リンティングのもう1つの典型的な用途は、IPプロバイダー、下請業者、およびオープンソースコミュニティからの外部コードのレビューを自動化することです。アルデックのALINT-PROは、VHDL、Verilog、およびSystemVerilog(デザインサブセット)で記述されたRTLコードの徹底した品質チェックを提供します。このチェックは、アルテックが開発したルール(ALDEC Basic, ALDEC Premium, ALDEC CDC, ALDEC SV, および DO-254)に加えて、日本のSTARC®(The Semiconductor Technology Academic Research Center)、Reuse Methodology Manual(RMM)が確立した一連のルールに対して実行されます。ALINT-PROは、設計チェック(ポリシー)の簡単なセットアップ、リンティングの実行、違反ルールの視覚化と除外、レポートの生成など必要な全ツールを組み合わせた独自のフレームワークを備えています。フレームワークは、ネットリストおよびCDC/RDCの問題分析のため、ネットリストの視覚化、クロックおよびリセットドメインの強調表示、クロックおよびリセットツリーの視覚化、検出されたクロックおよびリセットドメインクロッシングと同期回路へのナビゲーション、スケマティックやバイオレーションビューなどのデバッグウィンドウ間のクロスプローブなどの拡張デバッグ機能を提供します。同様に、ALINT-PROは、グラフィカルツール(FSMビューアー、FSMグラフ)を使用して、抽出された有限ステートマシンおよび検出された関連問題に対して直感的な診査機能を提供します。

フェーズ・ベース・リンティング(PBL)

フェーズ・ベース・リンティング(PBL)メソドロジは対応する問題の総数を減らし、デザインを修正・改良する回数を最小限に抑えることで、デザイン解析プロセスに明確な優先順位を付けます。従来の方法に比べてデバッギング時間が3~10倍速くなります。フェーズ・ベース・デザインルールチェックはオプションで、解析の順序を整理して同時に考慮される限られた数のデザイン問題に焦点を合わせます。

主な機能のまとめ

- フェーズ・ベース・リンティング・メソドロジはリンティングのフローに基づいて実装されています。

- リンティングのフローはプロセスです – 順序通りに実行・完了しなければならないフェーズのセットです。

- 各フェーズには固有のルールとパス基準があります(品質要求)。

- フェーズは定期かオプションにするか選択可能、各フェーズは特定のタイプの問題に対応。

- 定義済みのフロー・テンプレートが用意されています。最適化がなされていて、すぐに利用できます。

- フローテンプレートには、最も頻繁に実行されるタスクの便利なショートカットが含まれています。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.