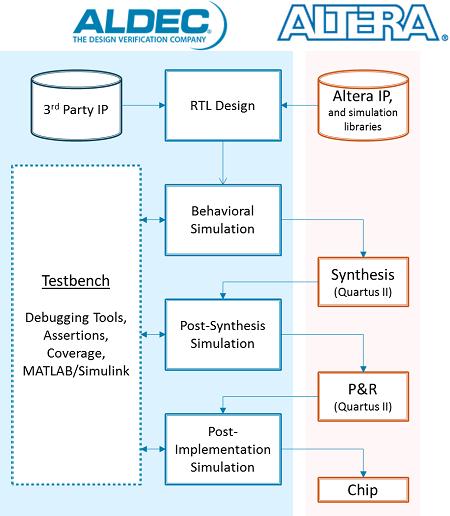

アルテラ (Altera) のデザインフロー

はじめに

アルデックのツールにはアルテラの全デバイスに対応したデザインツール、Quartus IIと接続するネイティブのインタフェースがあります。アルデックはアルテラと連携し、共通のお客様に、デバイスとライブラリのサポート、GUIの統一などについて統合的なサポートを展開しています。

デバイスファミリのサポート

アルデックのツールはアルテラのFPGAおよびSoCデバイスを、Cycloneファミリ、Arria、Stratixファミリなどを含め、すべてサポートしています。アルデックはアルテラのCPLDファミリ、MAXシリーズもサポートしています。

ライブラリのサポート

ユーザーはアルテラのEDAシミュレーションライブラリ・コンパイラユーティリティでシミュレーションライブラリをコンパイルできます。このユーティリティはActive-HDLとRiviera-PROを両方ともサポートしています。

アルデックはアルテラ向けにコンパイル済みのVHDL/Verilogライブラリも用意しており、いつでもアルデックのウェブサイトからダウンロードできます。

GUIの統合

アルデックのActive-HDLとRiviera-PROは、RTLシミュレーションとゲートレベルシミュレーションについて、アルテラQuartus IIに正式対応しているEDAシミュレータです。アルデックのツールでアルテラのデザインをシミュレーションする場合、作業環境の設定、シミュレーションライブラリのコンパイル、シミュレーション実行の順に進めていくことになります。

IPコアのシミュレーション

Quartus IIで生成したIPコアはすべてアルデックのツールでも使えます。Quartus IIはIPシミュレーション・スクリプトを生成するので、ユーザーはそのスクリプトでIPを直接シミュレーションできます。

レガシーデザインのインポート

アルデックはアルテラのMAX+PLUS IIソフトウェアからHDLのレガシーデザインをインポートする機能を持っています。レガシープロジェクトのどのようなHDLファイルでもまるごとアルデックのツールにインポートできます。そのHDLファイルを編集してアルテラの新しいデバイスにリターゲットすることもできます。

アルデックのシミュレータをデフォルトで使用する

プロセッサベースのシステムのシミュレーション

システムインテグレーション

アルデックの関連する製品

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.