トレーサビリティ

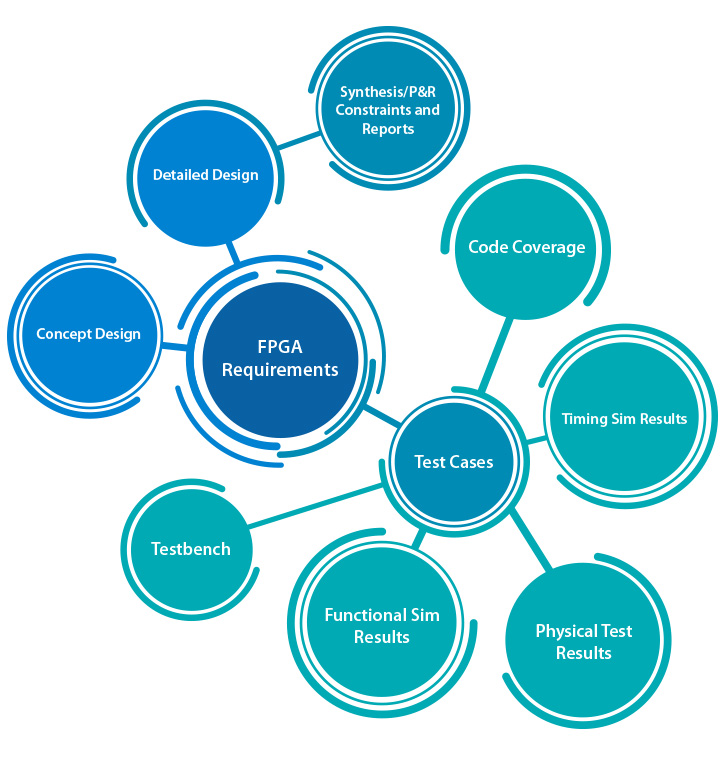

セーフティ クリティカルな設計では、要件がすべての設計および検証アクティビティの源となります。 さらに、要件と他のすべてのプロジェクト成果物との関係により、厳格な要件に基づいた設計および検証プロセスが守られていることの追跡、管理、実証することが可能になります。 このような関係をトレーサビリティデータと呼びます。

図 1. 要件と他のプロジェクト成果物との間の関係

トレーサビリティマトリックス

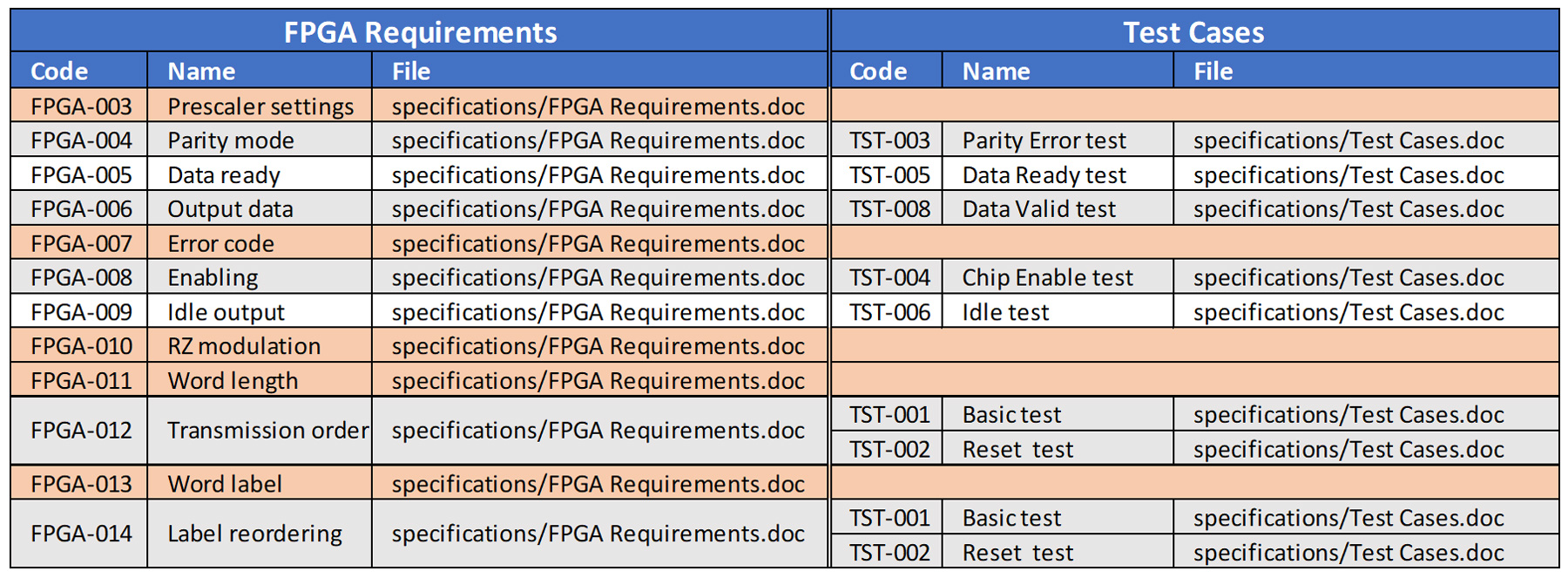

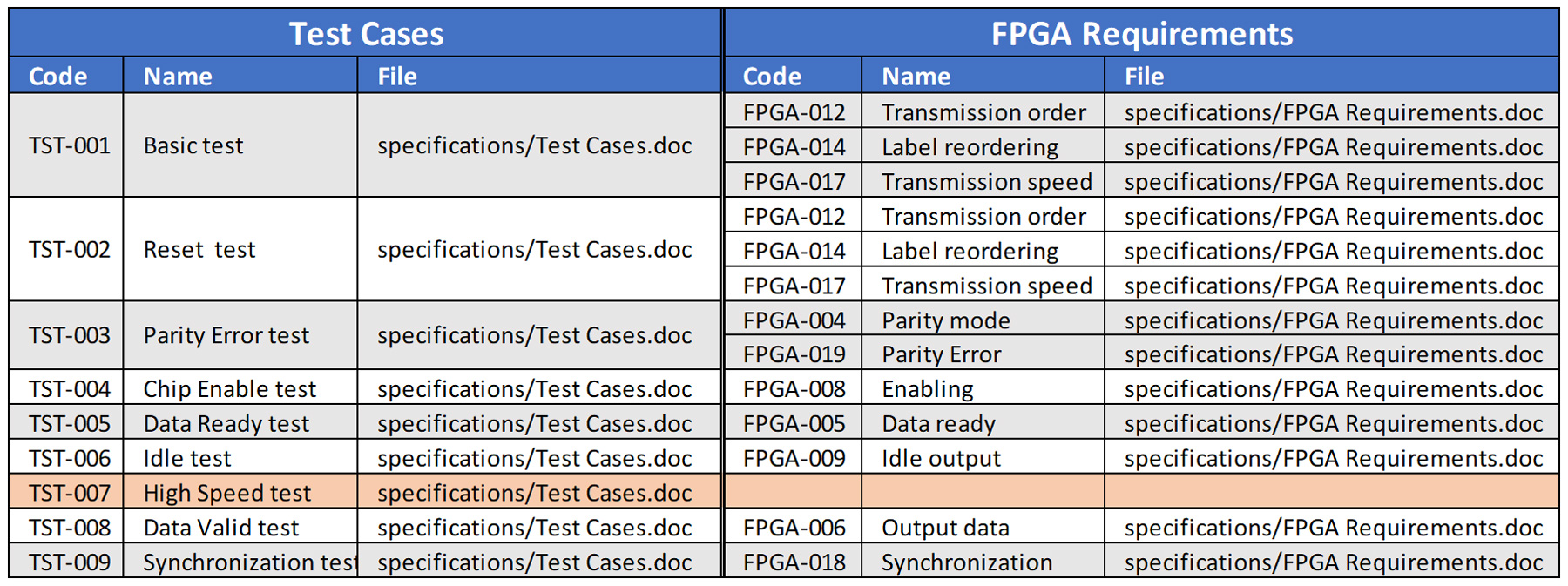

トレーサビリティマトリックスは、プロジェクト成果物のペア間の相関関係を示すスプレッドシートです。ハードウェア設計時に作成される最も一般的なマトリックスは以下の関係を示します:

- 回路カードアセンブリとFPGAの要件

- FPGAの要件とテストケース

- テストケース、テストベンチ、検証結果

- FPGA要件、概念設計および詳細設計

トレーサビリティマトリックスは、要件、設計、検証の各レベルでプロジェクトの完全性を示します。トップダウン方向のマトリックス(ダウンストリームトレーサビリティ) では、すべての要件の割り当て、実装、検証されていることを確認します。一方、ボトムアップビュー (アップストリームトレーサビリティ) では、未使用の要素が明らかになり、トレーサビリティデータ内の潜在的なギャップやエラーを発見する機会となります。

図 2. FPGA 要件とテスト ケースの間のトップダウン方向の関係

図 3. ボトムアップ方向の FPGA 要件とテスト ケースの関係

変更による影響解析

要件の変更は開発サイクルの一部であり、適切に管理されなければ最終製品の安全性に重大な影響を与える可能性があります。トレーサビリティマトリックスを適切に作成し維持することは、変更管理プロセスにとって非常に重要です。

Spec-TRACER™

Active-HDLで利用可能なアルデックのSpec-TRACERツールは、トレーサビリティの取得および分析プロセスを効率化して、各要件の完全実装、カバー、検証されていることを確認します。 要件カバレッジのギャップや未使用のHDLファンクションは、多方向のトレーサビリティマトリックスを使用して簡単に明らかにされ、レポートされます。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.