FPGAテスト・システム

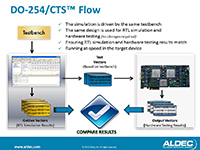

DO-254/CTSはターゲットボードによるテストを補強し、検証カバレッジを高め、DO-254/ED-80の検証目標を達成できるようにカスタマイズされたハードウェアおよびソフトウェアプラットフォームです。ターゲットデザインはカスタムドーターカードのターゲットデバイス上で実速度で実行されます。シミュレーションテストベンチをテストベクタとして使い、FPGAピンレベルで100%コントロール・監視しながら要求ベース検証を行い、通常範囲と異常範囲でのテストを実行できます。FPGAテスト結果を実速度でキャプチャし、シミュレータの波形ビューアに表示して高度な解析や文書化などに進むことができます。

主な特徴

|

Aldec, Inc.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.

Printed version of site: www.aldec.com/jp/products/mil_aero_verification/do-254