スタティック・デザイン検証

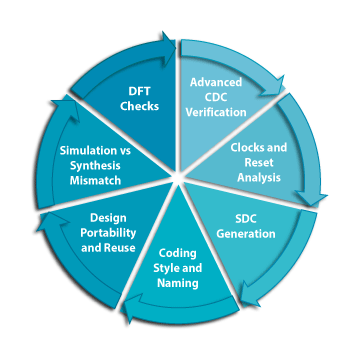

ALINT-PRO™はコーディングスタイルと命名規則、RTLと合成結果のシミュレーション不一致、スムーズで最適な合成、正しいFSM記述、 設計の後工程での問題、クロックおよびリセットツリーの問題、CDC、RDC、DFT、およびポータビリティと再利用のためのコーディングなどを中心に、VHDL、Verilog、SystemVerilogで記述されたRTLコードを解析する検証ソリューションです。このソリューションは、RTLとSDC™ソースファイルをベースにスタティック解析を行い、デザインの早期段階で重大なデザインの問題点を見つけ出し、設計時間の大幅短縮に貢献します。RTLシミュレーションおよび論理合成前にALINT-PROを実行すれば、デザイン上の問題をデザインフローの下流工程に波及する前に防ぎ、デザイン完成までに必要となる手戻りの回数を削減します。

DRCおよびCDC/RDC解析のための単一フレームワーク

ALINT-PROは、適切に設計された直感的なフレームワークで、RTLスケマティックビューア、FSMビューア、クロックおよびリセットビューア、コントロールスケマティックビューア、エラボレーションビューア、バイオレーションビューア、CDCビューアやRDCビューアなどの特別なツール、クロックおよびリセットドメインクロッシング解析のためのCDCスケマティックビューアを含む効率的なデザイン解析のための機能を提供します。

ALINT-PROは既存のHDLデザインの解析を行うためのセットアップで、外部プロジェクトファイル(Aldec Active-HDL、Aldec Riviera-PRO、Xilinx Vivado、Xilinx ISE、Intel Quartus)の読み込み、一般的なシミュレーションスクリプト (vcom、vlog、vsim、vlibなどの互換性コマンド)と、バッチモードツールの従来のファイルリストの解釈、個々のファイルとディレクトリ全体を直接インポート可能な非常にシンプルなGUIウィザードをサポートしています。

フルチップレベルリンティング 対 ユニットリンティング

ALINT-PROは、フルチップレベルリンティングとユニットリンティングの2つの異なるリンティング手法をサポートしています。両方の方法は互いに補完し合い、通常はデザインサイクルのさまざまな段階で適用されます。

フルチップレベルリンティングは、トップレベルインスタンスからリーフサブモジュールに伝播されるジェネリックパラメータの特定の値やユーザー定義のタイミング制約を適用し、デザイン全体の階層の解析を実行します。この手法では一般的なHDLリンティングツールでは伝統的であり、サインオフ期間中、またはシステムが統合された際にデザイン全体を一度に解析する必要がある検証タイプ(クロックおよびリセットチェック、CDC、RDC、DFT)でより頻繁に使用されます。この手法は、テスト対象のデザイン全体または少なくとも大部分が既に実装されていることを前提としています。

ユニットリンティングは、フラットなエラボレーションモード(HDLデザインユニットが互いに独立していると考え、ジェネリックパラメータのデフォルト値を使用する特別なエラボレーションモード)と組み合わせて使用する比較的新しいアプローチです。この処理スタイルは、まだ実装されていない階層ブロックなど、デザイン内の不足要素を非常に許容します。これにより、他ファイルと独立して、ファイルの変更直後などに各ソースファイルに適用する際にユニットリンティングが最も重要になります。そのため、非常に有用な多くのルールチェックがコード自体の記述直後の非常に早期の段階で適用でき、設計者の繰り返し作業を数日または数週間から数秒に絞ることができます。ユニットリンティングの自然なアプリケーションは、アルデックの最新バージョン Active-HDL™およびRiviera-PRO™で提供しているサードパーティ製の人気があるHDLエディタと同様のHDLエディタでバックグラウンド実行によるユニットリンティングとして統合しています。

独立したユニットの組合わせによって統合後に余分な問題が発生する可能性があるため、ユニットリンティングでは、従来のフルリンティングを使用する必要はありません。なお、ユニットリンティングを体系的に適用すると、サインオフ期間中の検証量を大幅に削減できます。

FPGAデザインのチェック

ALINT-PROは、最小限の設定でXilinx、Altera、Microsemi、およびLatticeテクノロジを使用したFPGAの実装をターゲットとするデザインのルールチェック実行をスムーズにサポートします。ALINT-PROは、FPGAベンダライブラリの最新バージョンを提供します。これらのライブラリは、事前にビルドされており、デフォルトでインストールされて、高度なタイミングおよびCDCルールチェック用に事前構成されています。

ALINT-PROは、IPベースのFPGAデザインの階層化とインクリメンタル解析フローのセットアップを自動化します。各IPブロックを事前に個々で解析し、抽出されたタイミング制約を促進して再利用することで、より高速で高レベルのデザイン解析を行うことができます。IPブロックが元デザイン環境で再構成されない限り、それ自体は一度だけ解析され、メインFPGAデザインの実行時の多くの時間を節約します。

バッチモードフロー

ALINT-PROの主要な機能は、TCLベースの豊富なスクリプトコマンドセットからもアクセスできます。このスクリプトを使用して、デザインルールチェック、設定の繰り返し、レポート生成を自動化できます。スクリプトは、インターラクティブコンソールシェルまたは完全自動バッチモードで実行できます。最後にALINT-PROは、最も一般的なデザイン入力とシングルコマンドラインシェル・アプリケーションコールを使用したバッチモードでのリンティングシナリオの実行可能で、これはJenkinsのような大規模なレグレッションテストスクリプトや継続的インテグレーション環境との統合に最適です。

ALINT-PRO™で利用できるルール・ライブラリ

ALINT-PROには、世界中の半導体企業が使用するデザイン開発のベストプラクティスを活用する、STARC(Semiconductor Technology Academic Research Center:半導体理工学研究センター)およびRMM(Reuse Methodology Manual)デザインガイドラインをベースにしたルールライブラリが含まれています。セーフティ・クリティカルなデザインについては、アルデックはデザインの安定性に影響を与える重要な問題の解析にフォーカスしたDO-254ガイドラインに基づくルールライブラリを提供しています。RISC-Vデザインコミュニティ向けに、アルデックは業界で実績のある最高のIPデザインプラクティスとガイドラインをベースにしたRISC-Vルールプラグインを提供しています。

メインルールプラグインは、アルデックのFPGAおよびASICデジタルデザインの社内経験に基づいており、さらに工業規模のデザインにおけるチップキラー問題と立ち向かう既存のALINT-PROのお客様からの多くの推奨する追加内容を、機能高度に設定可能なAldec BasicおよびPremiumルールライブラリで

補完しています。ALDEC SVプラグインは、SystemVerilogデザインサブセットに固有の新しい種類のRTLミスを対象としています。

ALINT-PROはALDEC_CDCルールプラグインによって、最新のマルチクロックおよびマルチリセットデザインでの複雑なクロックおよびリセットドメインクロッシング解析とメタスタビリティ問題対策の確認が可能なフルスケールCDCおよびRDC検証ソリューションになります。ALINT-PROの検証戦略は大きく分けて3つの要素:スタティック構造解析、デザイン制約の設定、ダイナミック機能検証で構成されます。最初の2つのステップはALINT-PROで実行し、ダイナミック機能検証は自動生成されたテストベンチを基に、ALINT-PROと連携するシミュレータ(Riviera-PRO™ , Active-HDL™, ModelSim®をサポート)上で実行されます。このアプローチは、ラボテストでしか検出できないようなRTLシミュレーション中に潜むメタスタビリティ問題を明らかにします。豊富な回路図およびHDEクロスプローブメカニズム、包括的なレポートおよびTCLベースAPIにより合成結果の確認、クロックとリセット構造、検出されたクロックとリセットドメインクロッシングと検出されたシンクロナイザを介して、CDCおよびRDCの問題のデバッグを実現しています。

主な機能

- クロック・リセット・ネットワークの解析

- RTLシミュレーションと合成後シミュレーションのミスマッチを防止

- FSM記述の正確性の検証

- 検出されたFSMのグラフィカルな解析と特定されたFSM問題

- コードのポータビリティと再利用性

- ALDEC_CDCルールプラグインによる幅広いCDCおよびRDCチェック

- 高度なCDCおよびRDCデバッグ環境

- スケマティックビューアー

- DFTチェック

- SDC™サポート

- IP記述用のデザイン制約拡張

- バックグラウンドおよびバッチ実行モード

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.