FPGAデザイン作成とシミュレーション

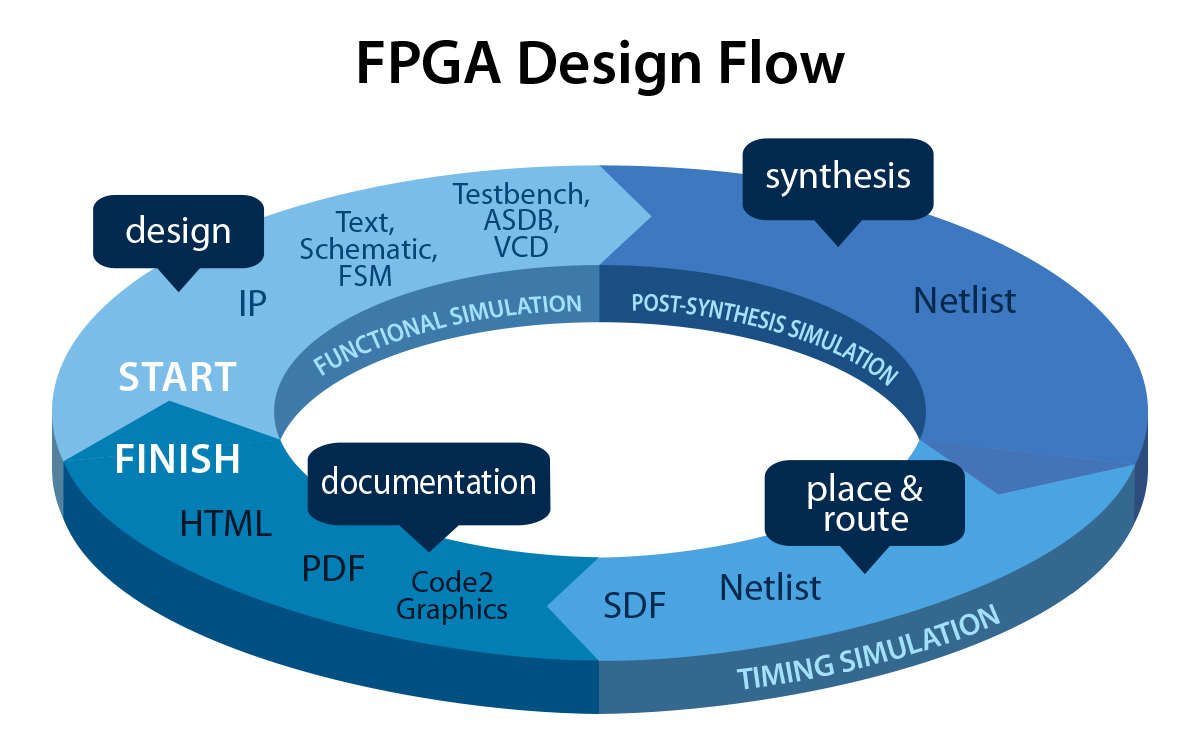

Active-HDL™はWindows®で動作するチーム環境向けFPGAデザイン作成およびシミュレーションの統合ソリューションです。Active-HDLの統合デザイン環境(IDE)には、完全なHDLおよびグラフィカル・デザインツールとRTL/ゲートレベルの混合言語シミュレータがあり、FPGAデザインを短期間で開発から検証までできるようになっています。

デザインフロー・マネージャはデザインエントリ、シミュレーション、合成およびインプリメンテーションの間で200種類以上のEDAツールやFPGAツールを起動できますので、開発チームはFPGAデザインプロセスにおいて一貫して同じプラットフォームを維持できます。Active-HDLはAMD、Intel、Lattice、Microchip、Quicklogicなど、主要なFPGAデバイスをすべてサポートしています。

主な機能と利点

-

チームベースの統一されたデザイン環境でローカルまたはリモート・チームにわたって統一性を維持可能

-

設定可能なFPGA/EDAフロー・マネージャインタフェースは200種類以上のベンダツールとインタフェースを取れるので、FPGA開発中一貫して1つのプラットフォームを使い続けられます

-

テキスト、スケマティックおよびステートマシンを活用してデザインを素早く作成

-

セキュアで信頼性の高い相互利用可能な暗号化規格でIPを配布・送付

-

共通カーネルの強力なVHDL/Verilog/SystemVerilog/SystemC対応混合言語シミュレータ

-

グラフィカルでインタラクティブなデバッギングとコード高品質化ツールでコードの品質と信頼性を確保

-

コードカバレッジ解析ツールで測定基準に基づく検証を実施、デザインの実行されない部分を特定

-

ABV(アサーションベース検証(SVA, PSL))で検証の質をアップ、より多くのバグを発見

- SV ファンクションカバレッジ、コンストレイントランダム、UVMなどの高度な検証構成をシミュレートする機能

-

HDLシミュレーションとDSPブロック用の高抽象度数学モデル環境のギャップはMATLAB®/Simulink®インタフェースで埋めます

-

HDL-スケマティックコンバータでデザインの核心部分を抜き出し分かりやすいグラフィックで表現

-

デザインドキュメントをHTMLやPDFで自動生成、すぐにデザインを共有可能

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.