HES-US-440 プロトタイピング、エミュレーションとHPCメインボード

プロダクトの詳細

キャパシティ

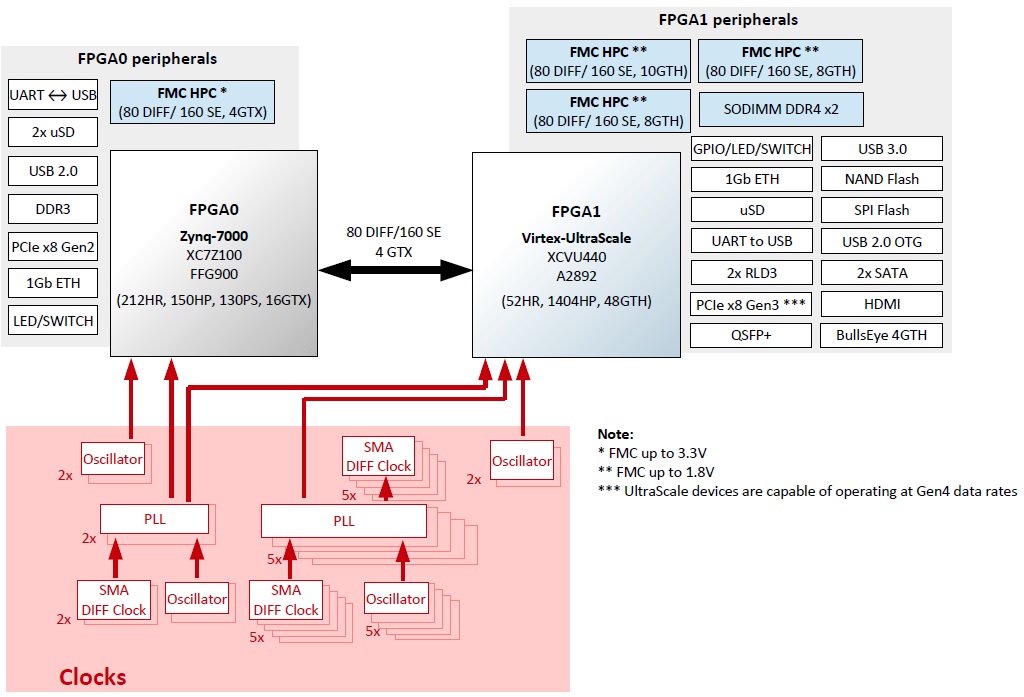

HES-US-440ボードは、Xilinx Virtex UltraScale XCVU440 ロジックモジュールとARMデュアルコアCortex-A9 CPUを搭載したXilinx Zynq-7000 ホストモジュールのユニークな組み合わせを提供し、デザインのためにワンボード・テストベンチを構築できます。最大2600万ゲートゲートの中規模ASICデザイン、または大規模FPGAデザインの高速物理プロトタイプとエミュレーションに最適化されています。このボードには、UltraScaleに接続された独立した2つのSO-DIMMスロットで最大64GBのDDR4とSRAMライクなインタフェースを備えた低レイテンシで総容量1152 Mbの2つのRLDRAM3モジュールが含まれています。 このようなメモリリーチボード設計により、物理的なプロトタイピング以外にも数多くのハイパフォーマンスコンピューティング (HPC) アプリケーションに適用できます。また、シミュレーション・アクセラレーションやバーチャルモデルを持ったコ・エミュレーションなどのHESエミュレーション・アプリケーションにも再利用できます。

クロッキング

非常に正確に設計されたクロッキング・ブロックは、任意の周波数に調節できる7つのクロック・ソースを提供し、そのうちの2つは両方のFPGAデバイスに配線された長さ調整済みのグローバル・クロック・ラインです。 グローバルクロックネットワークは、専用のSMAコネクタを介して外部ソースからドライブすることもできます。グローバルクロックに補足して、高速シリアルI / Oリンク(GTH、QSFP +、SATA)専用の3つの独立したクロックオシレータとDDRメモリ専用の4つのオシレータがあります。オンボードのクロック・ラインはすべて、LVDSシグナリングを使用してハイレベルのシグナル・インテグリティと波形消滅への耐性を保証します。

ホスティングとインタフェース

Xilinx Zynq-7000インターフェイスFPGAをXilinx UltraScale FPGAと同じボードに搭載することにより、次の2種類のホスティングアプリケーションを実装することができます:

- Zynqデバイスと組込みホスト :ARMコアで起動した組込みLinuxでUltraScaleに実装されたデザインのAMBA AXI/AHBバスをドライブ可能なテストベンチアプリケーションを実行

- 外部ホストPC :Zynqデバイスで、テストベンチアプリケーションを実行しているホストPCとUltraScaleに実装されたデザインを接続するPCIe-to-AXIブリッジを実行

いずれの場合もAldecは、HES Proto-AXIユーティリティバンドルに再利用可能なハードウェアおよびソフトウェアコンポーネントを提供します。組み込みホストシナリオの迅速な立ち上げのために、AldecはZynqデバイス用にすぐに使用可能なLinuxポートのイメージを提供します。外部ホスティングの場合、AldecのProto-AXI を使用することが可能で、AMBA AXIインタフェースを備えたインターフェイスモジュールIPとLinuxおよびWindows PC用の高抽象度のC++ APIを含むPCIe HESドライバで構成されています。

ボードには、次のような外部インタフェースも用意されています。PCIe gen3、USB 3.0とUSB 2.0 OTG、UART / USBブリッジ、QSFP +、1Gbイーサネット、HDMI、SATAとNANDの様な複数のフラッシュメモリ、SPIとMicro-SDなどのが含まれます。 標準のFMCコネクタを使用し、その他の特殊なインターフェイスやデバイスをドータカードで簡単に追加できます。

HES-US-440 プロトタイピング、エミュレーションとHPCメインボード

FPGA & Capacity

- Main FPGA: Virtex UltraScale XCVU440 (A2892 - 1456 I/O, 48 GTH)

- 26 Million ASIC Gates (estimated for 60% of FPGA utilization)

- Host FPGA: Zynq-7000 XC7Z100 (FFG900)

Flexible Clocking

- Total of 18 asynchronous clock generators

- 7 global clock modules with any-frequency clock synthesizers (Si5326)

- Base oscillators: 100 MHz, 2x 250 MHz, 2x 300 MHz, 2x 400 MHz

- SMA connectors for external clocks inputs and outputs

- 2 of global clocks connected to both UltraScale and Zynq FPGA

- Low-skew, length aligned clock lines

- 6 additional oscillators connected directly to UltraScale FPGA

- 4 separate oscillators dedicated to DDR4 and RLD3 memories (200 MHz)

- 2 general purpose oscillators 100 MHz, 200 MHz

- 2 additional oscillators connected directly to Zynq FPGA

- General purpose oscillators 100 MHz, 200 MHz

- 3 reference oscillators dedicated to high speed serial I/O

- 1 GTH reference oscillator: 156.25 MHz

- routed via fanout buffer (SY89468U) to both FPGAs

- 1 QSFP+ reference oscillator : 156.25 MHz

- 1 SATA reference oscillator: 150 MHz

- 1 GTH reference oscillator: 156.25 MHz

- 42 clock I/O of UltraScale FPGA available on FMC

- 13 clock I/O of Zynq FPGA available on FMC

Connectivity & Expandability

- Daughter card connectors (FMC-HPC)

- 3 FMC-HPC connected to UltraScale FPGA

- 480 I/O (240 DIFF) - standard GPIO optimized for LVDS & TDM

- 26 GTH - high speed serial I/O

- 1 FMC-HPC connected to Zynq FPGA

- 144 I/O (70 DIFF) - standard GPIO optimized for LVDS & TDM

- 4 GTX - high speed serial I/O

- 3 FMC-HPC connected to UltraScale FPGA

- Inter-FPGA connections

- 160 I/O (80 DIFF) - standard GPIO optimized for LVDS & TDM

- 4 GTX - high speed serial I/O

Memory Resources

- Memories connected to UltraScale FPGA

- up to 64 GB of DDR4 in 4 SO-DIMM slots (2 independent controllers)

- 1152 Mb of RLDRAM-3 in 2 modules

- SPI Flash, NAND Flash

- Micro-SD slot

- Memories connected to Zynq FPGA

- 1 GB of DDR3

- SPI Flash, EEPROM

- 2 Micro-SD slots

Interfaces & Hosting

- Host interfaces connected to Zynq FPGA

- PCIe x8, Gen 2

- USB 2.0

- UART/USB

- Other peripherals connected to Zynq FPGA

- I2C peripherals: RTC, Temperature Sensor, Accelerometer, EEPROM

- Misc: 4 LEDs, 8 Switches

- Peripherals connected to UltraScale FPGA

- PCIe x8, Gen 3

- Gigabit Ethernet

- QSFP+

- USB 3.0, USB 2.0 OTG, UART/USB

- SATA (2 slots)

- HDMI

- BullsEye GTH (4 lines)

- Misc: 11 LEDs, 10 Switches, 60 GPIO in 3 gold-pin connectors

- Board configuration and FPGA programming

- Programming from Host

- via USB 2.0 (Aldec Hes.Asic.Proto application)

- via JTAG (Xilinx utilities)

- via Digilent USB JTAG-SMT (Xilinx utilities)

- Programming from Micro-SD card or QSPI Flash

- Programming from Host

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.