アルデックは、HES-DVMの自動パーティショニングツールとHDLからFPGAへの コンパイル時間の短縮により、ASICデザインプロトタイプの立ち上げ時間を短縮しました

アルデックは、HES-DVMの自動パーティショニングツールとHDLからFPGAへのコンパイル時間の短縮により、ASICデザインプロトタイプの立ち上げ時間を短縮しました

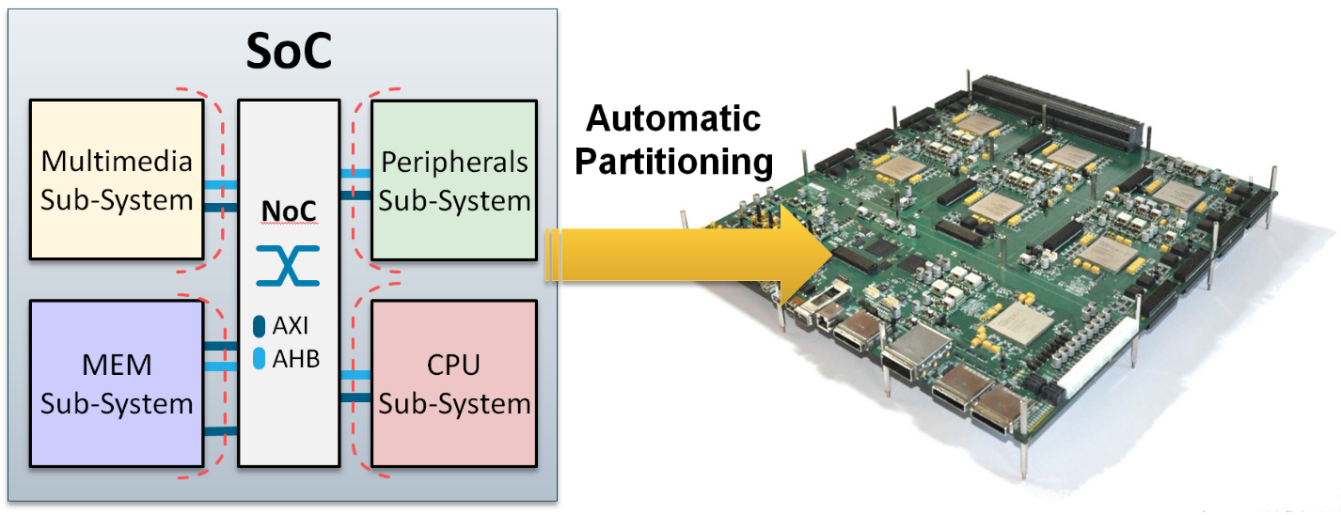

Henderson, NV, USA – 2019年9月24日 – HDL混在言語シミュレーションとFPGAおよびASICのハードウェア・アシステッド・ベリフィケーションのパイオニアであるAldec、Inc.(以下「アルデック」)は、SoCおよびASIC設計用の完全自動化およびスケーラブルなハイブリッド検証環境HES-DVM™に自動FPGAパーティショニングを導入しました。

従来はデザインの複雑さと制約の影響で、プロトタイピングに使用する複数FPGAへの手動分割には数日、場合によっては数週間掛かることがありましたが、HED-DVMの自動分割は数分でタスクを実行できます(調査、What-Ifシナリオでの理想)。

HES-DVMの最新リリースである2019.09も、アルデック独自のHDLコンパイラを備えています。SyntHESerと呼ばれ、今年初めに発表された最近の社内ベンチテストでは、約4500万ゲートのDeep Learning Accelerator(DLA)デザインの同一のHDLブロックを処理する場合、コンパイラは主要なスタンドアロンシンセシスツールよりも10倍高速に実行しました。

アルデックのハードウェア事業部ゼネラルマネージャー Zibi Zalewskiのコメント:

「HES-DVMへのこれらの追加は、ASICデザインのFPGAベースのプロトタイピングに関連する最大の挑戦の一部になります。ES-DVM 2019.09リリースでは、オンボードFPGAのパーティションの作成やマッチング、限られたFPGA I/Oリソースへの割り当てなど、最も退屈で挑戦的なアクティビティが完全に自動化されています。」

HES-DVM 2019.09リリースでは、アルデックのエンジニアはバランスの取れたパーティションの探索し、必要なインターコネクションを最小限に抑えることが可能な高速かつ効率的なアルゴリズムをデザインし実装しました。

「ユーザーはいつでもパーティション分割のプロセスにジャンプして、自動化アルゴリズムで円滑にパーティションとインターコネクションを変更できます」と、Zalewskiは付け加えます。

最後に重要性が最も低い手段ではないが、HES-DVMは、Xilinx Virtex® UltraScale™デバイスを使用するサードパーティボード向けに、Board Compiler(Verilog構造記述形式のファイルをインポートするのに用いられる)の導入を検討しています。この機能により、ユーザーは、FPGA間接続の追加または削除、テール(またはドーター)ボードとバックプレーンのハイブリッド構成を作成することにより、プロトタイピングボードを簡単に再構成できます。

Zalewskiは次のように結論つけています:

「HES-DVMのこれらすべての機能強化は、ASICまたはSoCのデザインライフサイクルの次の段階に入る前に、デザインに対する信頼性を低下させることなくエンジニアの時間を節約するために着手されたものです。またユーザーの要求に応じて行われるBoard Compilerを導入することにより、HES-DVMの汎用性を高め、他のボードで使用できるようにしました。」

新しいHES-DVM™2018.12ソフトウェアは現在入手可能です。 HES-DVMの詳細または評価についてはwww.aldec.comにアクセス、sales@aldec.comに電子メール、+1 (702) 990-4400に電話、またはAldecの世界各地の販売代理店にお問い合わせください。

アルデックは、HES-DVMの自動パーティショニングツールとHDLからFPGAへの コンパイル時間の短縮により、ASICデザインプロトタイプの立ち上げ時間を短縮しました

HES™ プロトタイピングについて

Aldecは、Xilinx Virtex UltraScaleおよびVirtex-7ファミリの最大サイズをベースにしたHES™ プロトタイピングボード のポートフォリオを提供しています。 これらのボードは、BPXバックプレーンと標準 FMCおよびBPX、ドーターカードコネクタを使用して簡単に拡張できるように設計されています。

HES-DVM™について

HES-DVM™は、SoCおよびASIC設計用の完全に自動化されたスケーラブルなハイブリッド検証環境です。SCE-MIやTLMなどの最新のコ・エミュレーション規格と最新のFPGAテクノロジを利用し、ハードウェアおよびソフトウェア設計チームはデザインのハードウェアプロトタイプへの早期アクセスを取得します。HES-DVMは、シミュレーションアクセラレーション、 ハイブリッドヴァーチャルプロトタイピング、 インサーキットエミュレーション、ソフトウェア検証とプロトタイピングを含むあらゆる種類のエミュレーションおよび物理プロトタイピング作業のために世界中のラボで使用されています

アルデックについて

アルデックは米国ネバダ州ヘンダーソンに本社を置く、エレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、SoC/ASICエミュレーション・プロトタイピング、デザインルールチェック、CDC/RDC検証、IPコア、要求ライフサイクル管理、DO-254機能検証、組込みソリューション、ハイパフォーマンスコンピューティングおよび軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.