SemiWiki: Clock Domain Crossing in FPGA

by Alex Tan

Clock Domain Crossing (CDC) is a common occurrence in a multiple clock design. In the FPGA space, the number of interacting asynchronous clock domains has increased dramatically. It is normal to have not hundreds, but over a thousand clock domains interactions. Let’s assess why CDC is a lingering issue, what its impact and the available remedy guidelines to ensure a robust FPGA design.

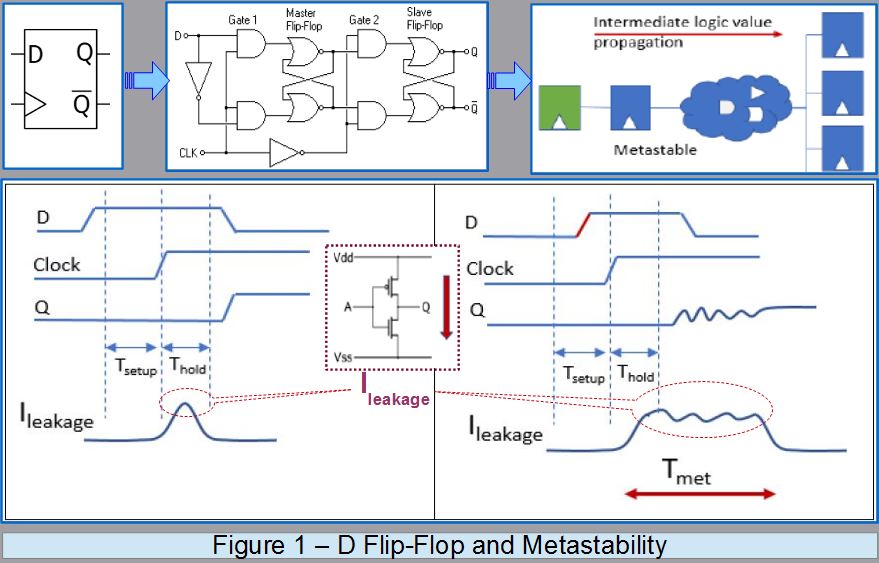

CDC occurs whenever data is transferred from a flip-flop driven by one clock to a flip-flop driven by another clock. CDC issues could cause significant amount of failures in both ASIC and FPGA devices. The consequence of CDC is a metastability effect which leads to either functional non-determinism (unpredictability of downstream data, which could also yield to data loss) or data incoherency (when CDC induced delayed latency on subset of bus signals being sent across, causing non-uniform capture event).

For the rest of this article, please visit SemiWiki.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2025 Aldec, Inc.