SoC FPGA設計に関わるハードウェア・ソフトウェアエンジニアを援護するアルデックのQEMU Bridge

アルデック、仮想プロセッサエミュレータを統合した協調シミュレーション環境をサポート

Henderson, NV – 2017年11月15日 – エレクトロニクス設計検証のインダストリ・リーダーである Aldec, Inc.,(以下「アルデック」)は、QEMU Bridge を追加したRiviera-PRO™の最新版をリリースしました。アルデックの先進的検証プラットフォームであるRiviera-PROは、これによりSoC FPGA上で動作することを意図したデザインのハードウェア・ソフトウェア協調検証ができるようになりました。

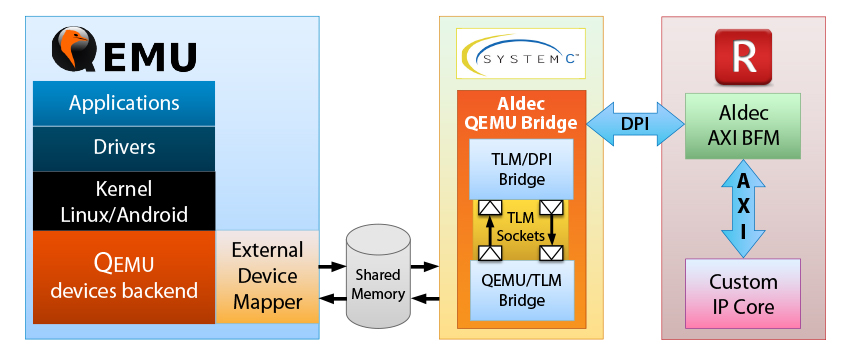

FPGAのカスタムIPやソフトウェアアプリケーションやドライバをQEMUの仮想プロセッサ上で統合してシミュレーションすることが簡単にできるようになりました。QEMU Bridge はSystemC TLMトランザクションをAXIに変換したり、その逆を行い、高速なコシミュレーション 用インタフェースとなります。

アルデックのソフトウェアプロダクトマネージャ Radek Nawrotのコメント:

「デザインが大規模化しデバイスが複雑化することで、システムインテグレーションは難易度が上がっています。QEMUを導入すれば協調シミュレーションが円滑になり、ハードウェアとソフトウェアのエンジニアは協力し合いながら開発サイクルの早い段階でバグを探し、特定して消せるようになります。そのため開発時間と費用の削減につながります。」

Riviera-PROを使用するハードウェアエンジニアはHDLにブレークポイントを設定したり、データフローを検証したり、さらにはコードカバレッジやQEMU上で実行中のソフトウェアアプリケーションから実行されるパスなどを解析したりすることができます。QEMUを使用するソフトウェアエンジニアはGNU Debugger (GDB) でブレークポイントを使ってコードを行ったり来たりしながら、カーネルとドライバを両方とも検証できるようになります。

このソリューションに関するデモ映像は、QEMUとRiviera-PROでHDLとソフトウェアの協調シミュレーションをご覧ください。

Riviera-PRO 2017.10の新機能には他にも次のようなものがあります:

- インラインのランダム呼び出しを含むコードがある場合のパフォーマンスが大幅に向上

- UVMデザインのシミュレーションは最大29%高速化

- VHPIデザインシミュレーションの高速化

- デザインルールチェックツールALINT-PRO™とダイレクトに接続

- ミックスド・シグナルSilvaco® SmartSpice™インタフェース(初期段階)

- コンパイル済みのAldec AXI BFM 1.7

- プロットウィンドウでヒストグラムの作成が可能

その他詳細、チュートリアル、概要プレゼンテーション、新機能、無料評価版のダウンロードなどにつきましては、ウェブサイト http://www.aldec.com/Products/Riviera-PROをご覧ください。

Riviera-PROについて

Riviera-PRO™は最先端のFPGA/SoCデバイスを設計するエンジニアの検証ニーズに応えます。Riviera-PROは、高性能シミュレーションエンジンとあらゆる抽象レベルでの先進的なデバッグ能力、それに最新の言語と検証ライブラリ規格のサポートをひとつにすることで、テストベンチの生産性、再利用性、および自動化を極限まで進めます。

アルデックについて

アルデックは1984年に設立されたエレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、ハードウエア・アシステッド・ベリフィケーション、SoC/ASICプロトタイピング、デザインルールチェック、IPコア、要求ライフサイクル管理、DO-254機能検証、組込みソリューション、および軍事/航空宇宙向けソリューションなどの分野で、パテントを取得したテクノロジを提供しています。www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.