アルデック、DVCon Europe 2017でFPGAプロトタイピングのソフトウェア駆動テストを発表

Munich, Germany – 2017年10月9日 – ASIC/FPGAデザイン向けHDL混合言語シミュレーションとハードウェア・アシステッド・ベリフィケーションのパイオニアである Aldec Inc., (以下「アルデック」)は、10月16~17日にドイツのミュンヘンで開催される DVCon Europe Conference and Exhibition で、「チュートリアル: FPGAプロトタイピングのソフトウェア駆動テスト」を発表します。

チュートリアル:「FPGAプロトタイピングのソフトウェア駆動テスト」

日程: 10月16日(月)午後2:00~3:30 フォーラム7にて

講師: Krzysztof Szczur(Aldec Inc.)、Radosław Nawrot(Aldec Inc.)

概要:

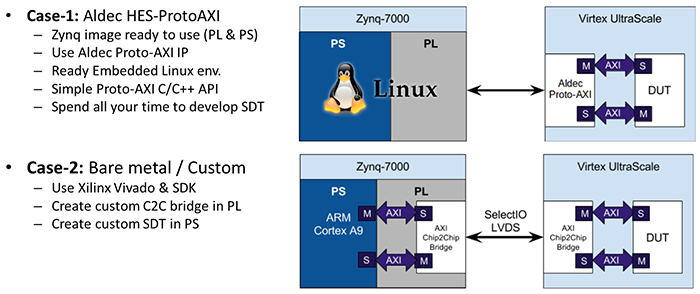

現在のFPGAの技術革新はASICデザインからの知見を採り入れながらSoCの来た道をたどっています。今では、Xilinx® Zynq™ のようにARM CortexとリコンフィギュラブルなFPGAを1チップに詰め込んだハイブリッドデバイスもあります。これらのデバイスはFPGAにプロトタイプしたデザインへの組込みソフト駆動のテストベンチとして使えるくらい融通が利きます。ZynqのようなデバイスはFPGAリソースが限られていますが、約2,600万ASICゲート分の容量を持つ Xilinx UltraScale(XCVU440)のようなFPGAをボードに追加することもできるので、容量の面では障害にはなりません。

このチュートリアルでは、ソフトウェア駆動のテストシナリオを実行する組込みテストベンチをどう強固に構築するかについて説明します。また、AMBA AXI インターコネクトなどSoCのテストに適用できる色々な接続オプションを紹介し、アルデックのProto-AXIインタフェースとプロトタイピングボード「HES-US-440」を使ってデモンストレーションをします。このボードにはデザイン用に Virtex UltraScale XCVU440、ソフトウェア駆動テストベンチ組込み用に Zynq XC7Z100 を搭載しています。

アルデックのブース #404で、実際のベリフィケーションスペクトラムをご覧ください。

- シミュレーション - UVMをサポートする高機能混合言語シミュレータ

- DRC/CDC解析 - デザインルールチェック(DRC)とクロックドメイン交差(CDC)検証を統合したプラットフォーム、SystemVerilogデザインルールもサポート

- エミュレーション – ハードウェア・アシステッド: インサーキット・エミュレーション、仮想プロトタイプとの協調エミュレーション、UVMシミュレーション・アクセラレーション

- 物理プロトタイピング – 複数のFPGAへのデザイン・パーティショニング技術を応用したSoC・ASIC・ASSPのプロトタイピング

アルデックについて

アルデックは米国ネバダ州ヘンダーソンに本社を置く、エレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、ハードウェア・アシステッド・ベリフィケーション、SoC/ASICプロトタイピング、デザインルールチェック、CDC検証、IPコア、要求ライフサイクル管理、DO-254機能検証、組込みソリューションおよび軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。 www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.