アルデック、ASICデザインのパーティショニングの課題を解決するHES-DVM Protoモードを提供

Henderson, Nevada, U.S.A. – 2017年9月11日 – ASIC/FPGAデザイン向けHDL混合言語シミュレーションとハードウェア・アシステッド・ベリフィケーションのパイオニアであるAldec, Inc.(以下「アルデック」)は、HES-DVM™ ソフトウェアの最新版を発表しました。この最新版では、シミュレーション・アクセラレーションモード、エミュレーションモードに加えて、新しいプロトタイピングモードが搭載されました。

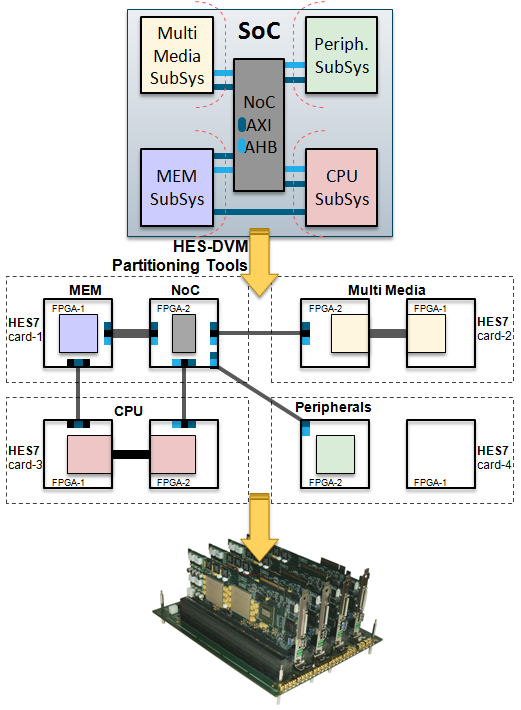

この新しい HES-DVM Proto では、新しいパーティション設計・接続ツールが導入されました。プロトタイピングエンジニアと検証エンジニアは、複数のFPGAで構成された複雑なプロトタイピング・プラットフォーム上でデザインを実行する際に最大のクロック周波数を得るために、パーティショニングの自動化と制御範囲の理想的なバランスを取らなければなりません。HES-DVM Proto は最近増えているこのような要望に応えるツールです。

今回の HES-DVM™ 2017.09 リリースでは、色々なパーティショニングのシナリオを迅速に検証し、所定のプロトタイピングボードで最高性能を出せるパーティショニングを決められます。便利なGUI表示と影響解析ツールで、必要な接続、利用可能な接続が見えるので、ボトルネックをすぐに見つけ、さらにパーティショニングを改善するかボードをカスタマイズして解消することができます。

マルチFPGAでのパーティショニングではI/Oとボードレベルの相互接続が限定されるという問題が共通してありましたが、HES-DVM™ の最新リリースはこの問題を解消します。アルデックはコンフィギュラブルなチップ間接続モジュールを自動挿入しやすくすることでこの問題を解決しました。このモジュールはSERDESモジュールとLVDS信号を用いて現在のFPGAで出せる最大の転送速度を実現しています。さらに、ゲーテッドクロック自動変換機能でASICデザインを確実にFPGAにインプリメントしやすくなりました。

新しいHES-DVM ProtoモードはアルデックのHESプロトタイピング・プラットフォームだけでなく、Virtex-7™ や Virtex UltraSCALE™ FPGAを(複数個)搭載したサードパーティのボードもサポートします。

アルデックのハードウェア部門ゼネラルマネージャの Zibi Zalewski のコメント:「今回、HES-DVM Protoのリリースを発表できて嬉しく思います。これは弊社のFPGAプロトタイピングとエミュレーションのソリューションを補完するものです。デザインをマルチFPGAのプロトタイプとしてセットアップする機能を持ち、何ヶ月もかかる退屈な作業をなくします。FPGAテクノロジをここまで使い倒せるEDAメーカーは弊社だけです。同じFPGAプロトタイピングボードをシミュレーション・アクセラレーションにも、仮想プラットフォームとの協調エミュレーションにも利用できて、しかも物理プロトタイピングも簡単になりました。」

もっと詳しく知りたい方は、間もなく開催されるアルデックのウェブセミナー「Aiding ASIC Design Partitioning for multi-FPGA Prototyping(マルチFPGAプロトタイピングでのASICデザイン・パーティショニングの支援)」をご視聴ください。

販売について

最新の HES-DVM™ 2017.09 は現在販売中です。詳しい内容を知りたい方、評価をご希望の方は、アルデック・ジャパンのメールアドレス sales-jp@aldec.com または電話番号03-5312-1791までお問い合わせください。

HES™ プロトタイピングについて

アルデックは Xilinx の Virtex UltraScale と Virtex-7 ファミリの最大規模のFPGAを搭載したHES™ プロトタイピングボードのシリーズを提供しています。ボードはBPXバックプレーンと標準のFMCとBPXドーターカードコネクタで簡単に拡張できるような構成になっています。

HES-DVM™について

HES-DVM™ はSoC/ASICデザイン向けの全自動かつスケーラブルなハイブリッド検証環境です。SCE-MIやTLMのような最新の協調エミュレーション規格や、最新鋭のFPGAテクノロジを活用し、ハードウェアとソフトウェアそれぞれの設計チームがデザインのハードウェアプロトタイプをすぐ入手できるようにします。HES-DVMは世界中の検証の現場で、シミュレーション・アクセラレーション、ハイブリッド・バーチャルプロトタイピング、インサーキットエミュレーション、ソフトウェア検証、プロトタイピングなど、あらゆる種類のエミュレーションタスクと物理プロトタイピングの用途に活用されています。

アルデックについて

米国ネバダ州ヘンダーソンに本社を置くアルデックは、エレクトロニクス・デザイン検証のインダストリ・リーダです。RTL設計、RTLシミュレータ、ハードウエア・アシステッド・ベリフィケーション、SoC/ASICプロトタイピング、デザインルールチェック、CDC検証、IPコア、要求ライフサイクル管理、DO-254機能検証および軍事/航空宇宙向けソリューションといったパテントを取得したテクノロジを提供しています。www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.