### **UVM Transaction Debugging**

- TLM Introduction

- Transaction visualization in Riviera-PRO

- Transaction recording in UVM

- Graphical Debugging for TLM and UVM in Riviera-PRO

- UVM-TLM simulation example demo

## Introduction

- As size of typical digital design grows, you have to raise *abstraction level* while creating it.

- Higher abstraction levels can be achieved in different areas:

- When handling individual bits is no longer feasible, you can use arrays, records/structures or even associative arrays.

- When simple functions/tasks/procedures are not enough to manage your code, you can switch to **Object Oriented Programming** (OOP).

- When data transferred in your design gets too diverse and too complicated, you should consider raising data transfer abstraction to *Transaction Level*...

### **Transactions Overview**

- *Transaction* is an abstraction of information transfer.

- If you have a problem with the term transaction, try to replace it with message.

- In languages supporting OOP transaction is typically executed by calling method of some design object.

In other languages it can be a procedure/function call.

- In UVM a transaction is a class object (*uvm\_transaction*), that includes whatever information is needed to model the communication between two components.

- The amount and detail of the information encapsulated in a transaction is an indication of the abstraction level of the model.

## **Basic TLM Communication**

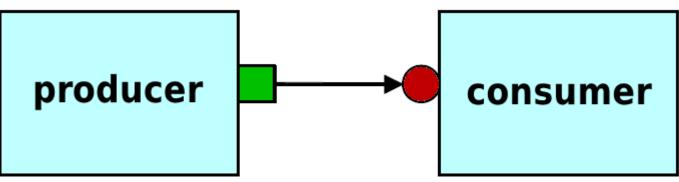

- The most basic transaction-level operation allows one component to put a transaction to another

- The producer generates transactions and sends them out through its *port* (green square).

- The actual implementation of the transaction is supplied by the consumer.

- The transaction implementation (in consumer) connects with requester via *export* (red circle).

##

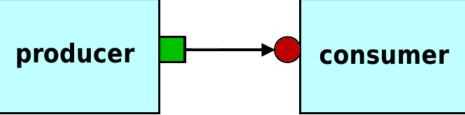

If directions of data and control flow agree, *producer puts transaction into consumer*:

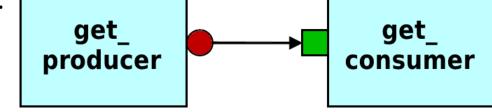

If directions of data and control flow disagree, consumer gets transaction from the producer:

No matter if it is *put* or *get* situation, the process with *export* (the executor) is responsible for implementation of the transaction; requester is using its *port* to call services of the executor.

- Simple transaction models (direct consumer to producer connection) work OK only when data traffic is slow.

- It may be necessary for components to operate independently, where the producer is creating transactions in one process while the consumer needs to operate on those transactions in another.

- TLM *FIFO* is used to synchronize data flow between producer and consumer.

- So, the producer puts the transaction into the TLM FIFO fifo, while the consumer independently gets the transaction from the FIFO.

## **Analysis Ports**

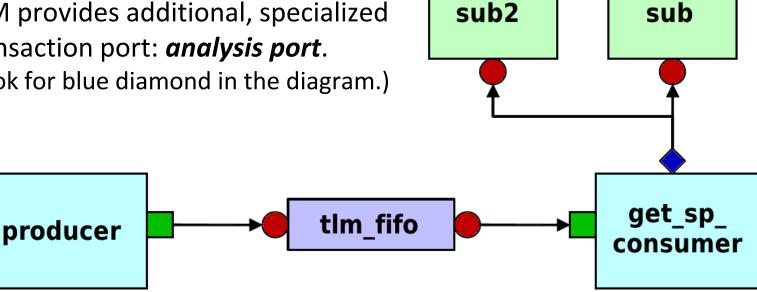

TLM provides additional, specialized transaction port: *analysis port*. (Look for blue diamond in the diagram.)

tlm analysis port has just one interface method write (void function) and can be connected to analysis exports of multiple data-collecting components (scoreboards, coverage collectors, etc.)

## **Transaction Recording in Riviera-PRO**

- The transaction defined in the source code can be recorded in the simulation database in Riviera-PRO.

- The transaction happens on a transaction stream.

- Transactions have both their beginning and end times and can overlap one another.

| Name            | Value | 0, 10, 20, 30, 4 | ۱ <mark>۵</mark> | 50 60 70    | 80 | 90  100  110 | 120 | p30, p40, p | 50  160 |

|-----------------|-------|------------------|------------------|-------------|----|--------------|-----|-------------|---------|

|                 |       | Count Relations  |                  |             |    |              |     |             |         |

| packet stream   |       |                  |                  |             |    |              |     |             |         |

|                 |       | <b>⊞</b> 120     |                  | <b>⊞</b> 34 |    | B 238        |     | B 211       |         |

|                 |       |                  |                  |             |    |              |     |             |         |

|                 |       | Count Relations  |                  |             |    |              |     |             |         |

|                 |       |                  |                  |             |    |              |     |             |         |

| stream_consumer |       |                  |                  | m or        | 7  | III. 222     | 1   | III out     |         |

|                 |       | <b>⊞</b> 120     |                  | BB 34       |    | B 238        |     | B 211       |         |

|                 |       |                  |                  |             |    |              |     |             |         |

|                 |       |                  |                  |             |    |              |     |             |         |

### **Transaction Attributes**

- The transaction attribute is a user-defined property assigned to a transaction.

- An attribute has a name and a value.

- Attributes can be assigned any arbitrary meaning.

| lame                                              | Value           | 0, , 10, 20, 30<br><b> </b> |                   |

|---------------------------------------------------|-----------------|-----------------------------|-------------------|

| packet_stream<br>addr<br>accept_time<br>initiator | 120<br>0<br>467 | ■ 120<br>0<br>467           | B 34<br>40<br>487 |

## Linking Signals to a Transaction

- Signals could be linked to a transaction stream.

- Easy association between the transactions and the signals.

- Linked signals are automatically traced in asdb.

| Name               | Value   | 0, , 20, 40, 60, 80, 1 | 100   120    | 140     | 160 180  | 200     | 220     | 240 2       | 60  2 | 280   300   32 | 0,  340,  360, |

|--------------------|---------|------------------------|--------------|---------|----------|---------|---------|-------------|-------|----------------|----------------|

|                    |         | 韋 🔲 Count 📝 Relations  |              |         |          |         |         |             |       |                |                |

| ABUS               |         |                        |              |         |          |         |         | ABUS        |       |                |                |

| type               | WRITE   |                        | B WRITE      |         |          | ] [     | E READ  | )           |       |                |                |

| addr               | 1284    |                        | 1284         |         |          |         | 1241    | 6           |       |                |                |

| data               | 1928    |                        | 1928         |         |          |         | 1031    |             |       |                |                |

| relations in( 0 )  |         |                        | relations ir | (0)     |          |         | relatio | ons in( 0 ) |       |                |                |

| relations out( 0 ) |         |                        | relations o  | ut( 0 ) |          |         | relatio | ons out( 0  | )     |                |                |

| R= rewr            | 0       |                        |              |         |          |         |         |             |       |                |                |

| R= req             | 1       |                        |              |         |          |         |         |             |       |                |                |

| R= grant           | 0       |                        |              |         |          |         |         |             |       |                |                |

| R= ack             | 0       |                        |              |         |          |         |         |             |       |                |                |

| ⊳ R= data          | 0000000 |                        | 0000000      |         | 00000788 | 0000000 | )0      |             |       | 00000407       | 00000000       |

| ⊳ <b>R</b> = addr  | 0000000 |                        | 0000000      |         | 00000504 | 0000000 | )0      |             | ) (   | 00003080       | 0000000        |

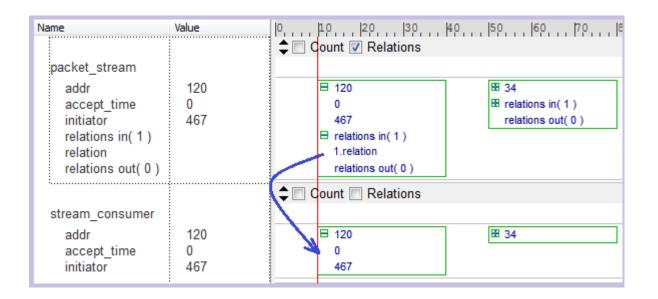

### **Linking Transactions**

- Two transactions can be related as source transaction and target transaction.

- Helps with better understanding of the data flow in the design.

- The relation interpretation is abstract and up to the user.

## **Using Transaction Recording**

Simple case using Riviera-PRO's transaction recording functions.

```

task doXaction (abus ibus);

trans1 = $beginTransaction ( my stream, $time);

tmp = ibus.addr;

$addAttribute( trans1, "addr", tmp );

tmp = ibus.data;

$addAttribute( trans1, "data", tmp );

tmp = ibus.write;

$addAttribute( trans1, "write", tmp );

#100

$endTransaction ( trans1, $time );

endtask

initial begin

abus t:

my stream = $createStream ("ABUS");

t = new;

t.randomize();

doXaction(t);

```

| Name                          | Value          | 0               |

|-------------------------------|----------------|-----------------|

| ABUS<br>addr<br>data<br>write | 58<br>266<br>0 | Count Relations |

### www.aldec.com

end

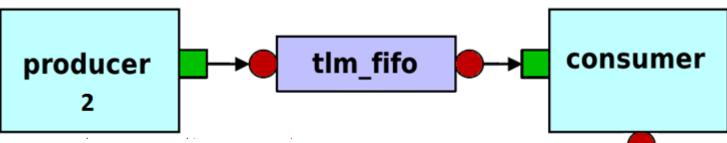

## **Transaction Recording in UVM**

Let's take a look at UVM's sample design: 'Hello World'.

- The design contains two producers, consumer and FIFO:

- 1<sup>st</sup> producer talks to consumer directly.

- 2<sup>nd</sup> producer talks to consumer via tlm\_fifo.

- Producers generate randomized packets and sends them via ports.

- Consumer receives packets and generates transactions .

## **'Hello World'- Top level connections**

```

class top extends uvm_component;

```

```

producer #(packet) p1;

producer #(packet) p2;

uvm tlm fifo #(packet) f;

consumer #(packet) c;

`uvm component utils(top)

function new (string name, uvm_component parent=null);

super.new(name,parent);

p1 = new("producer1",this);

p2 = new("producer2",this);

f = new("fifo",this);

= new("consumer",this);

С

p1.out.connect( c.in );

p2.out.connect( f.blocking_put_export );

c.out.connect( f.get export );

endfunction

```

endclass

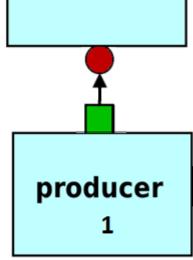

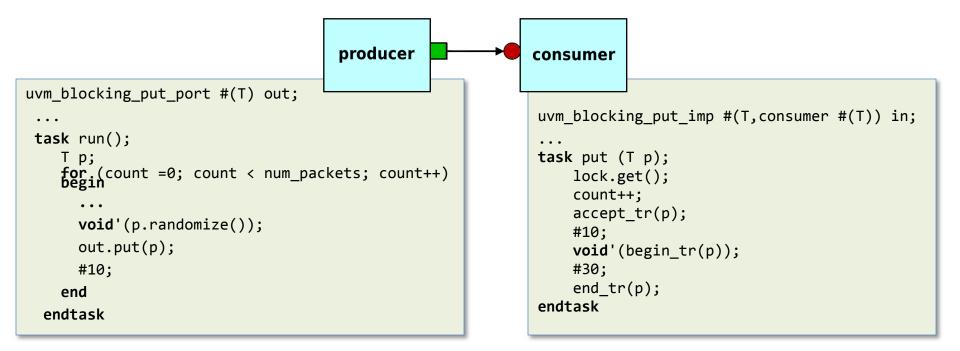

## **Direct Port/Export Connection**

- Producer 1 connects to Consumer directly: port to export.

- Producer 1 makes call to put() function.

- Consumer provides implementation for put() function.

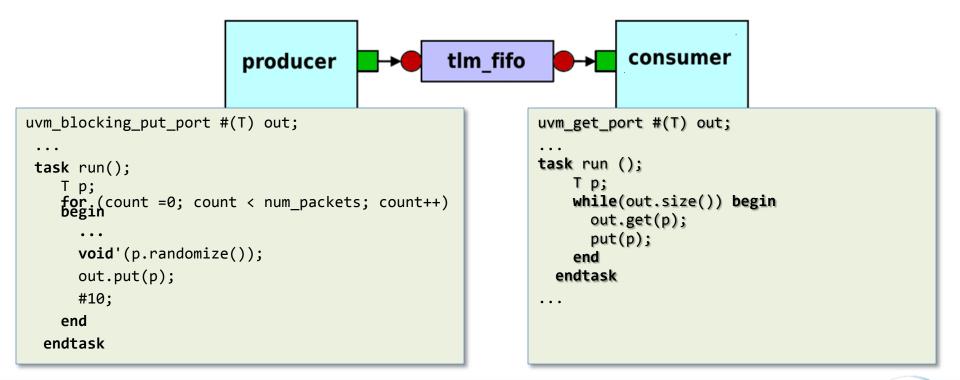

## **Connection via TLM-FIFO**

- Producer 2 connects to Consumer vial TLM FIFO.

- Producer and consumer operate independently.

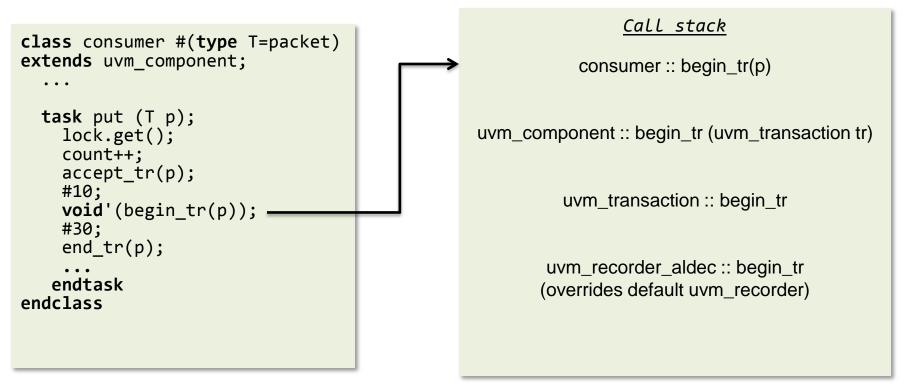

## 'Hello World' - Consumer

Let's have a closer look at the transaction implementation in UVM starting with the Consumer.

## uvm\_recorder\_aldec Class

- Default uvm\_recorder class provides methods (functions) with basic recording functionality for the transactions

- simple output to a text file.

- uvm\_recorder\_aldec extends uvm\_recorder with

- Transaction recording to Aldec's simulation database.

- This enables visualization of transactions on the waveform.

- Using uvm\_recorder\_aldec

- If no recorder object is instantiated in Consumer uvm\_default\_recorder will be used

- To override instantiate global\_recorder\_aldec in Consumer:

```

task run_phase(uvm_phase phase);

...

this.recorder = global_recorder_aldec;

```

### **Attributes Recording**

- A user does not have to worry about specifying each property of the transaction object he/she wants to be recorded.

- The following UVM techniques take care of it:

- 1. Register object properties with `**uvm\_field\_int** macro.

```

class packet extends uvm_transaction;

rand int addr;

endclass

```

```

class consumer #(type T=packet) extends uvm_component;

```

```

`uvm_component_utils_begin(consumer #(T))

`uvm_field_int(count,UVM_ALL_ON + UVM_READONLY + UVM_DEC)

`uvm_component_utils_end ...

```

## Attributes Recording – cont.

2. Consumer calls end\_tr()

uvm\_transaction::end\_tr()

uvm\_object ::record -

\_\_\_\_m\_uvm\_field\_automation () – automatically extracts all the fields

uvm\_recorder\_aldec :: record\_field

uvm\_recorder\_aldec :: set\_attribute

\$addAttribute(...); - Aldec's PLI function to record the

transaction attribute in the simulation database (asdb)

## **'Hello World' Example – output**

| Name                | Value    | 0, ,  10, ,  20,<br>Count Caller |      | , ,  7º, , ,  8º, , ,  9º, , ,  1º | о, " 110, " 120, " 130, " 140, " | <u> </u> |

|---------------------|----------|----------------------------------|------|------------------------------------|----------------------------------|----------|

| stream_consumer     |          |                                  |      |                                    | stream_consumer                  |          |

| addr                | 120      | ⊟ 120                            | ⊟ 34 |                                    | ⊟ 211                            | ⊟ 188    |

| accept_time         | 0        | 0                                | 40   | 80                                 | 120                              | 160      |

| initiator           | 467      | 467                              | 487  | 467                                | 487                              | 487      |

| I                   |          | Count 🔲 Relation                 | ons  |                                    |                                  |          |

| packet_stream       |          |                                  |      |                                    | packet_stream                    |          |

| addr<br>accept_time | 120<br>0 | 目 120<br>0                       | ₩ 34 | ₩ 238                              | ₩ 211                            | ₩ 188    |

| initiator           | 467      | 467                              |      |                                    |                                  |          |

| {INFO}/producer.sv(46) @ 0 ns: top.producer2 [producer] Starting.                          |

|--------------------------------------------------------------------------------------------|

| {INFO}/producer.sv(62) @ 0 ns: top.producer2 [producer] Sending producer2-0                |

| {INFO}/producer.sv(46) @ 0 ns: top.producer1 [producer] Starting.                          |

| {INFO}/producer.sv(62) @ 0 ns: top.producer1 [producer] Sending producer1-0                |

| {INFO}/producer.sv(62) @ 10 ns: top.producer2 [producer] Sending producer2-1               |

| {INFO}/producer.sv(62) @ 20 ns: top.producer2 [producer] Sending producer2-2               |

| {INFO}/consumer.sv(57) @ 40 ns: top.consumer [consumer] Received producer1-0 local_count=1 |

| {INFO}/producer.sv(62) @ 50 ns: top.producer1 [producer] Sending producer1-1               |

| {INFO}/consumer.sv(57) @ 80 ns: top.consumer [consumer] Received producer2-0 local_count=2 |

| {INFO}/producer.sv(62) @ 90 ns: top.producer2 [producer] Sending producer2-3               |

|                                                                                            |

## **Graphical Debugging in Riviera-PRO**

### 1. Call Stack window

| 🔁 Ca | l Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                     | \$2×                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| In   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | File                                                                                                                                                                                                | Line                                         |

|      | record ( this={{{{producer1-0} 00000242} {{{{} 0000024}<br>end_tr ( this={{{{consumer} 00000222} {000000C8 {{}<br>put ( this={{{{consumer} 00000222} {000000C8 {{{00<br>put ( this={{0000001 LOOP 00000000 {{{{{in} 0000}<br>put ( this={{0000001 {{0000001 LOOP 00000000 {{}<br>run_phase ( this={{{{run} 000001 LOOP 00000000 {{}<br>run_phase ( this={{{{run} 000004D} 000001D3} {000000<br>exec_task ( this={{{{run} 000004D} 0000014 UVM_}<br>@FORK#3003_0@ ( this={{{{run} 000004D} 0000004D} 000000<br>Apackage uvm_pkgVuvm_task_phase/@INTERNAL#> | C:/Aldec/Riviera-PRO-201)<br>C:/My_Designs/UVM/alde0<br>C:/Aldec/Riviera-PRO-201)<br>C:/Aldec/Riviera-PRO-201)<br>C:/My_Designs/UVM/alde0<br>C:/Aldec/Riviera-PRO-201)<br>C:/Aldec/Riviera-PRO-201) | 2802<br>58<br>85<br>83<br>67<br>2565<br>3011 |

### 2. Watch window

| ර්් Watch 1                                                                                                  |                                                                                      | \$≥                                          | ×   |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|-----|

|                                                                                                              |                                                                                      | ▼ ⊗ a?* Attributes                           | -   |

| Name                                                                                                         | Value                                                                                | Туре                                         | Las |

|                                                                                                              | <pre>{{{} 0000001} 0000000 0000002 {tr_<br/>{{} 0000001} 0000000 00000002 {tr_</pre> | . – –                                        | Â   |

| <ul> <li>P_ recorder.[uvm_recorder].[uvm_object]</li> <li>P_ recorder.[uvm_recorder].recording_de</li> </ul> | {{} 0000001}                                                                         | [uvm_object]<br>int S                        |     |

| Precorder.[uvm_recorder].file                                                                                | 00000002<br>{tr_db.log}                                                              | UVM_FILE S<br>string                         |     |

| •∎ recorder.[uvm_recorder].tr_handle ▶ •∎ recorder.[uvm_recorder].default_radix                              | 2.7532E+008                                                                          | real<br>uvm_radix_enum S                     | Ε   |

| recorder.[uvm_recorder].physical recorder.[uvm_recorder].abstract                                            | 1                                                                                    | bit<br>bit                                   |     |

| recorder.[uvm_recorder].identifier                                                                           |                                                                                      | bit                                          |     |

| <ul> <li>Precorder.[uvm_recorder].policy</li> <li>Creation Corder.[uvm_recorder].scope</li> </ul>            | UVM_DEFAULT_POLICY<br>{{initiator} {NULL}}                                           | uvm_recursion_policy_enur<br>uvm_scope_stack | ÷   |

| · · · · · ·                                                                                                  | m                                                                                    | •                                            |     |

## **Graphical Debugging – cont.**

### **3.** Transaction Data Viewer

|   | - Begin Time - 💌 🔊 al 🖅 🎉 |          |      |             |           |            |  |  |

|---|---------------------------|----------|------|-------------|-----------|------------|--|--|

|   | Begin Time                | End Time | addr | accept_time | initiator | < relation |  |  |

| 1 | 10ns                      | 40ns     | 120  | 0           | 468       | 1          |  |  |

| 2 | 50ns                      | 80ns     | 34   | 40          | 488       | 1          |  |  |

| 3 | 90ns                      | 120ns    | 238  | 80          | 468       | 1          |  |  |

| 4 | 130ns                     | 160ns    | 211  | 120         | 488       | 1          |  |  |

| 5 | 170ns                     | 200ns    | 188  | 160         | 488       | 1          |  |  |

| 6 | 210ns                     | 240ns    | 72   | 200         | 488       | 1          |  |  |

### 4. Waveform

| lame          | Value | ю.,, <u>р</u> о,,,, | 20  30    | 40  50  60  70  80 |  |

|---------------|-------|---------------------|-----------|--------------------|--|

|               |       | 韋 📃 Count           | Relations |                    |  |

| packet_stream |       |                     |           |                    |  |

| addr          | 120   | <b>⊟</b> 120        |           | ⊟ 34               |  |

| accept_time   | 0     | 0                   |           | 40                 |  |

| initiator     | 467   | 467                 |           | 487                |  |

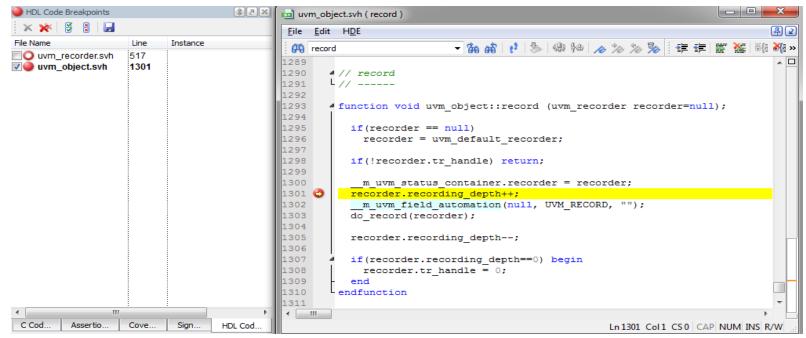

## **Graphical Debugging –cont.**

### 5. Breakpoints and single stepping

6. Class Viewer is coming soon...

## Summary

- Start using UVM in your Testbench

- UVM provides mechanism for doing many things automatically, recording transactions is one of them

- Aldec enhances UVM recording function with graphical visualization of transactions

#### Founded 1984 (Privately Held)

Aldec

#### **Corporate Headquarters**

2260 Corporate Circle Henderson, NV USA

#### **Office Locations**

Katowice, Poland Kharkov, Ukraine Paris, France Tokyo, Japan Shanghai, China Taipei, Taiwan Bangalore, India Raanana, Israel Worldwide Distribution

### **Technology Patents**

**US Patent#5,479,355:** System and method for a closed loop operation of schematic designs with electrical hardware

US Patent#5,051,938: Simulation of selected logic circuit designs

**US Patent#4,827,427:** Instantaneous incremental compiler for producing logic circuit designs

US Patent#4,791,357: Electronic circuit board testing system and method

**US Patent#7,003,746**: Method and apparatus for accelerating the verification of application specific integrated circuit designs

**US Patent#6,915,410**: Compiler synchronized multi-processor programmable logic device with direct transfer of computation results among processors

# Website:<a href="http://www.aldec.com">http://www.aldec.com</a>Tel. USA:+1-702-990-4400E-mail:sales@aldec.comTel. Europe:+33-6-80-32-60-56E-mail Europe:sales-eu@aldec.comWebinars:http://www.aldec.com/events

### Products

### GDI Active-HDL<sup>™</sup>

- FPGA Design and Simulation Made Easy

- PRO Riviera−PRO<sup>™</sup>

- Fast RTL Simulation Engine

#### ALINT<sup>™</sup>

Design Rule Checking

### HES™

Emulation, Acceleration and Prototyping System

### **Military and Aerospace Solutions**

#### DO-254/CTS™

### DO-254 Functional Verification Solution

Actel<sup>™</sup> Prototyping Adaptors RTAX-S/SL and RTSX-SU Rad-Tolerant, Space-Flight System Designs