Starting Active-HDL as the Default Simulator in Intel Quartus II

Introduction

Active-HDL simulator can be run directly from Intel® Quartus software using NativeLink feature. This application note explains how to use the NativeLink feature in Intel Quartus II. This application note has been verified on Active-HDL 10.3 and Quartus 16.1. This interface allows users to run mixed VHDL, Verilog and System Verilog (“design” constructs) simulation using Active-HDL as the default simulator.

Configuring Active-HDL in Quartus II

Open your design in Intel quartus II and compile all source files.

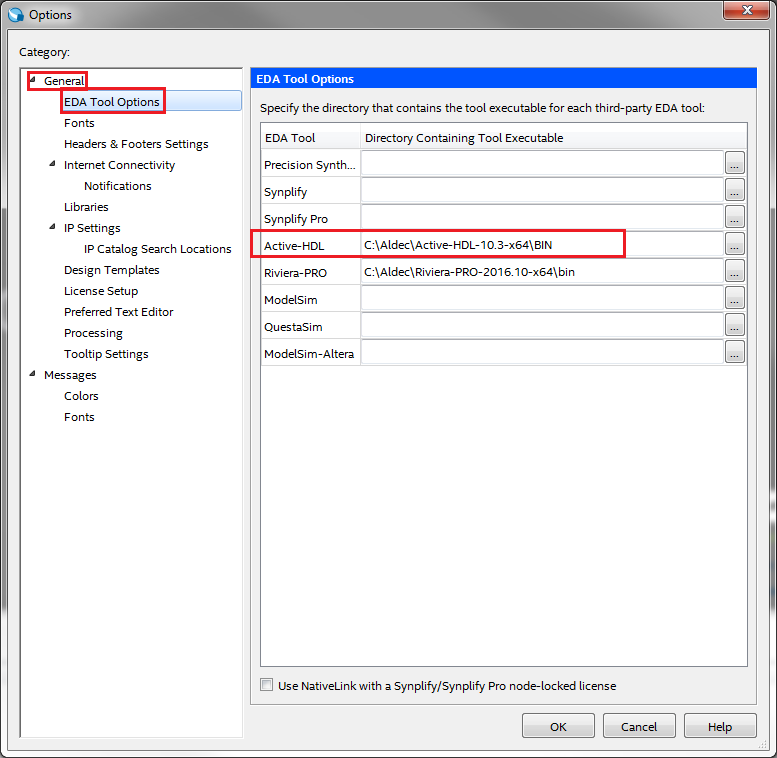

In Quartus II, Open the Options window using Tools | Options. Select the EDA Tools Options under the General category. Under the Active-HDL entry, select a path to the \bin folder in your Active-HDL installation.

Figure 1 EDA Tool Options

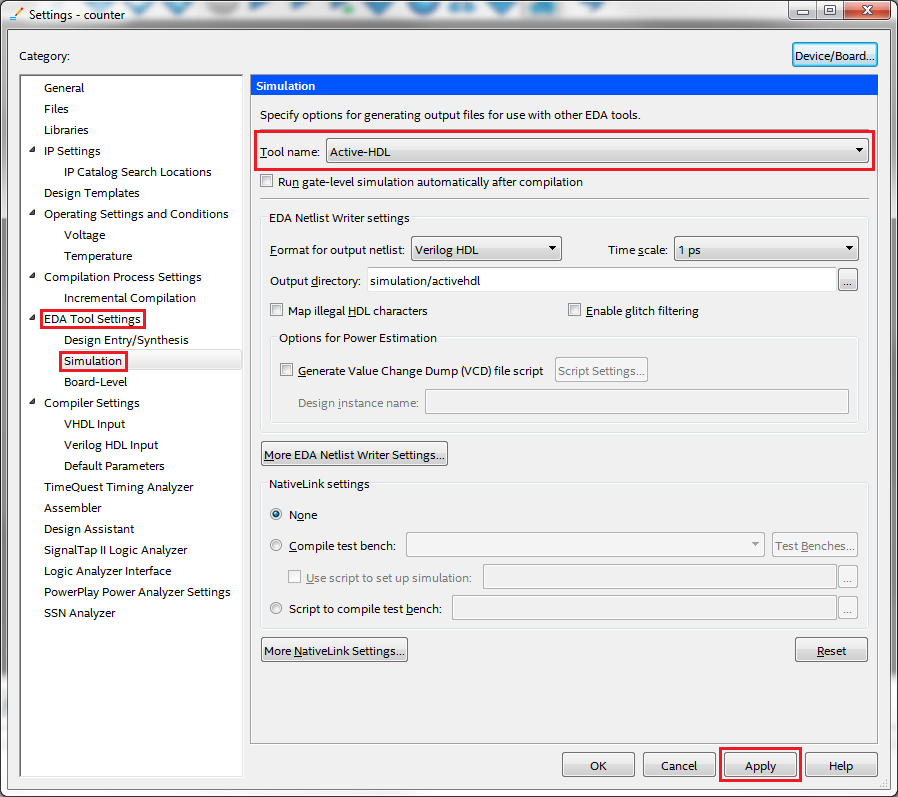

Now go to menu Assignments | Settings. Here, select Simulation category under EDA Tool Settings. On the right hand side, in the Tool name drop down box, select Active-HDL as shown in figure 2 and click Apply.

Figure 2 EDA Tool Settings in Quartus II

NativeLink Settings

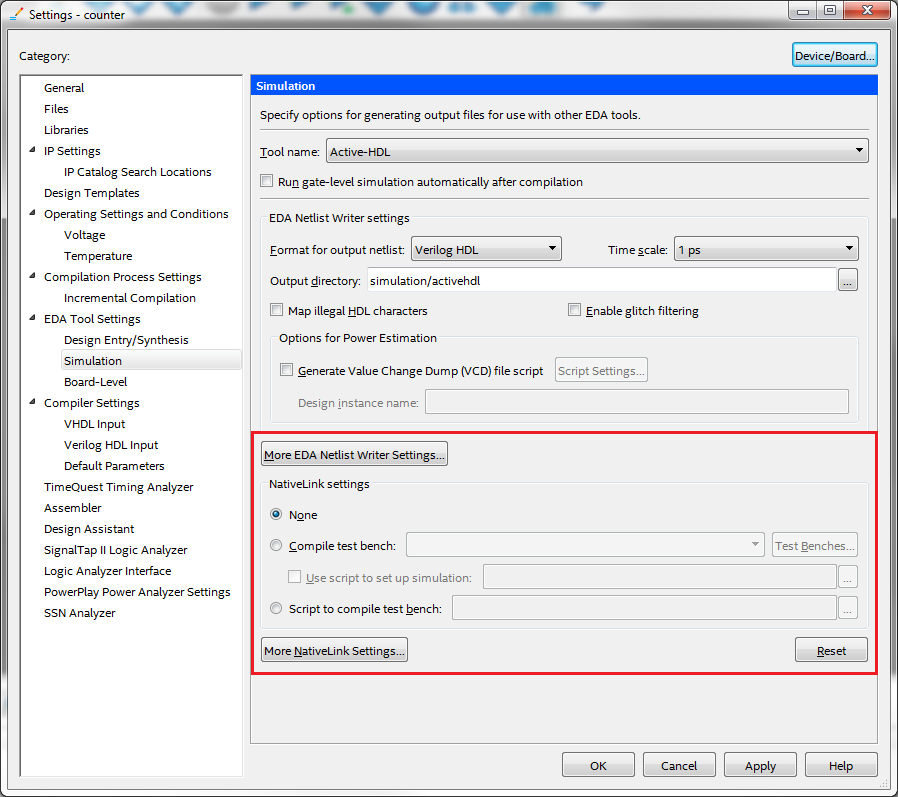

NativeLink settings are located at the bottom of Simulation category on the right hand side, as shown in Figure 3. There are three NativeLink settings for selecting the test bench for the simulation.

None — Turns off the test bench option. When Active-HDL opens, you will have to add the test bench, compile it and run the simulation manually. Other project files will be added to Active-HDL automatically.

Compile test bench — Allows you to select a test bench that is compiled during simulation, if you have created one or more test benches.

Use script to set up simulation — Allows you to specify a script file containing commands for the running Simulation in Active-HDL. In this case, When Active-HDL opens; it calls and runs this script which may contain commands for test bench compilation and simulation.

Figure 3 EDA Tool Settings

Now select the option of your choice from NativeLink Settings. For Running the simulation, please refer to the next section. For more details on these options please click on the link at the end of this application note.

Running the simulation

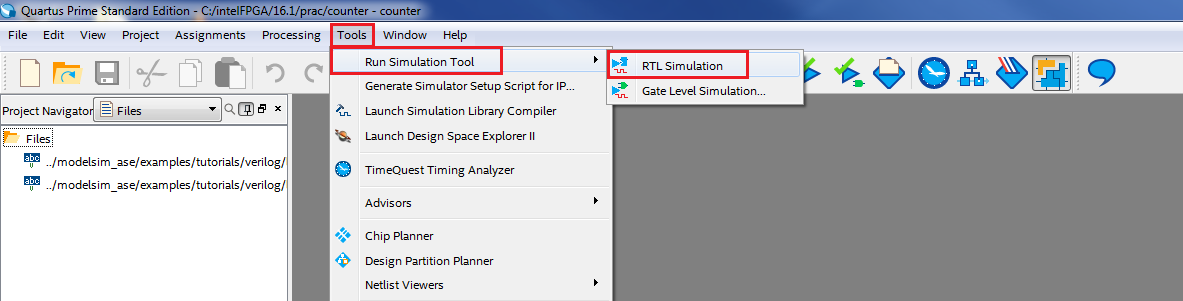

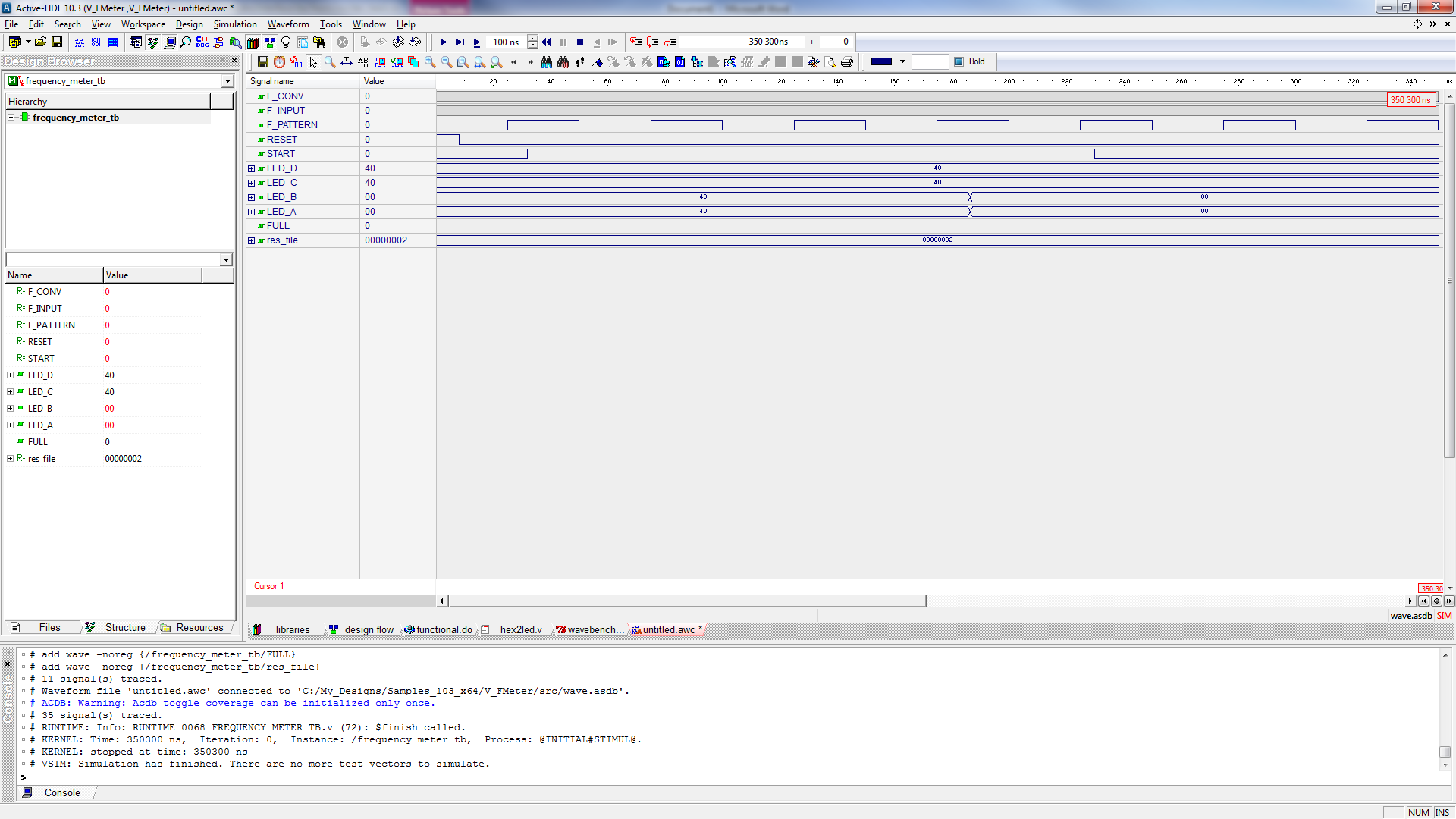

To launch Active-HDL from Quartus II, click on Tools | Run Simulation Tool | RTL Simulation option. Active-HDL starts and creates the project and adds necessary files to the project. It also creates and compiles the necessary Intel libraries. It adds signals to the waveform and runs simulation after that. You will receive the end of the simulation message in the console when simulation is done as shown in Figure 4.

Figure 4 Running Simulation

Figure 5 Running Simulation

More information

For detailed information on starting and running Active-HDL simulator from Quartus II software please visit, http://www.altera.com/literature/hb/qts/qts_qii5v3.pdf.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.