Performing Functional Simulation of System Created with Qsys in Active-HDL

Introduction

This document describes the steps required to run functional simulation of Intel/Altera Qsys design in Active-HDL. It has been verified on Qsys delivered with Quartus Prime Standard Edition 17.0 and Active-HDL 15. The Qsys System Design Tutorial is used to demonstrate the flow.

Requirements and Limitations

This application note assumes the following:

You have the following software installed and licensed:

Intel/Altera Quartus® II version 14.1 or later, and all necessary devices from Intel

Active-HDL 10.1 or later

You have downloaded the Qsys tutorial design example (tt_qsys_design.zip) used in this application note. You can download it from the Platform Designer Tutorial Design Example web page.

You have followed the instructions provided in the Generate a Testbench System in Qsys chapter of the Qsys System Design Tutorial and have generated the rivierapro_setup.tcl script.

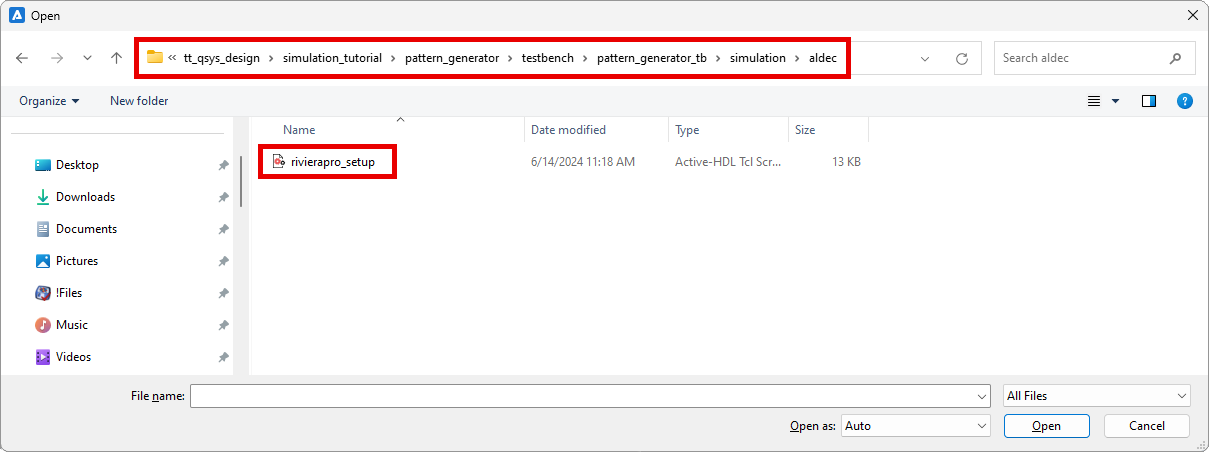

Running Simulation of Qsys Design

Once you generate the simulation models in Qsys, the rivierapro_setup.tcl script is generated in the tt_qsys_design/simulation_tutorial/pattern_generator/testbench/pattern_generator_tb/simulation/aldec folder.

Open Active-HDL. Change the location to point to the rivierapro_setup.tcl script. Execute the following command from the Console:

cd <path to the design>/tt_qsys_design/simulation_tutorial/pattern_generator/testbench/pattern_generator_tb/simulation/aldec

where:

<path to the design> - points to the folder where you extracted the tt_qsys_design_zip archive.

Figure 1. Accessing the Qsys script in Active-HDL.

Open the rivierapro_setup.tcl script. Execute the following command from the Console:

open -do rivierapro_setup.tcl

This script sets up all necessary environment variables and declares the aliases that compile required libraries, compile design files, and initialize simulation. The script can be executed as is, or you can modify any of the aliases according to your needs. The table below provides the description of the alias commands:

Alias

Description

dev_com

Compiles device library files.

com

Compiles design files.

elab

Elaborates the top level design and initializes simulation. The top level design is defined in the script by the TOP_LEVEL_NAME variable.

elab_debug

Elaborates the top level design with optimizations disabled (-dbg and -o2 are passed to asim) and initializes simulation.

ld

Compiles all libraries and design files, elaborates the top level design, and initializes simulation.

ld_debug

Compiles all libraries and design files, elaborates the top level design, and initializes simulation with optimizations disabled (-dbg and -o2 are passed).

Table 1. Aliases defined in the rivierapro_setup.tcl script.

Navigate to the line of code where the following expression is checked in the condition of the if statement:

[ string match "Active" $Aldec ]

The QSYS_SIMDIR variable needs to be updated in the statement body so that it pointed to the correct location after loading the design in Active-HDL. The statement should look as follows after applying this modification:

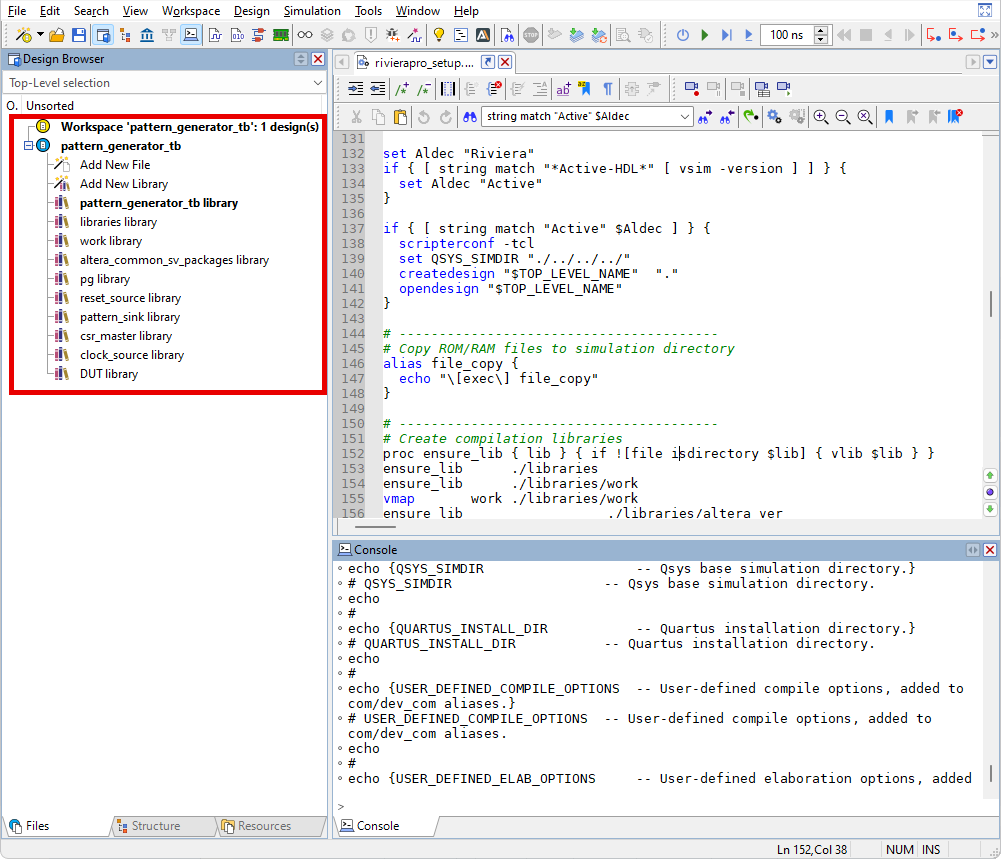

if { [ string match "Active" $Aldec ] } { scripterconf -tcl set QSYS_SIMDIR "./../../../" createdesign "$TOP_LEVEL_NAME" "." opendesign "$TOP_LEVEL_NAME" }

Run the script. Execute the following command from the Console:

do rivierapro_setup.tcl

Once the script is executed, the new design will be created and activated.

Figure 2. The system created with Qsys loaded into Active-HDL.

Execute the dev_com command from the Console.

NOTE: You can skip this step if you have already installed the Intel libraries, including the libraries for the device family used in the generated design.

This will compile the following libraries:

altera_ver

lpm_ver

sgate_ver

altera_mf_ver

altera_lnsim_ver

cycloneive_ver (depends on a device family in use)

Execute the com command from the Console. This will compile design source files.

Execute the elab command from the Console. This will initialize the simulation.

Run the simulation by executing the run 40us command from the Console.

NOTE: You can instantiate your top module (which contains your Qsys module) inside the generated testbench file in order to simulate your entire design.

Conclusion

Intel Qsys designs can be successfully simulated in Active-HDL. To get detailed information about creating a system with Intel Qsys, refer to the following link:

https://www.intel.com/content/www/us/en/docs/programmable/683364/18-1/creating-a-system-with.html

If you have difficulty simulating the Qsys design in Active-HDL, please contact Aldec Support via customer portal.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.