Simulating Xilinx MicroBlaze design using the Active-HDL Simulator

Introduction

This Application Note describes how to use Aldec's Active-HDL to simulate a Xilinx MicroBlaze design.

This Application note assumes that you have created the hardware part of your embedded system as well as the software to run on it in Xilinx ISE and EDK and that you have built your embedded design in Xilinx Platform Studio and integrated it with ISE project. Your complete chip level project in ISE may include non-XPS based blocks. Further, we will explain how to simulate your complete Xilinx ISE design (which may include both XPS and non-XPS blocks) in Active-HDL.

Note: This application note assumes that you have ISE Design Suite 14.7 and Active-HDL 10.2 or later properly installed and licensed.

To simulate your system you will need to generate a simulation model of your embedded design.

Follow steps to generate simulation models

Before you can generate a simulation model for your embedded design, you have to get EDK simulation libraries provided by Aldec for Active-HDL.

Click on http://www.aldec.com/en/downloads to get the library package.

Log in to portal using your email ID and password. If you are not registered then please register using ‘Register’ button on same page.

Once you are logged in, click on Active-HDL > version number (for e.g. 10.2) > windows32 > XILINX LIBRARIES

Now download EDK library (.zip file) matching your ISE version and Active-HDL version.

If you cannot find the necessary library version please submit your request to Aldec support team by opening a support case at http://www.aldec.com/support/index.php with the version number of EDK and Active-HDL that you intend to use.

Once the EDK library package is received, extract it from the zip archive and store it on the local disk. e.g. C:\Aldec\Active-HDL-10.2\vlib\EDK147

You can then use Active-HDL to simulate your embedded system design at behavior level.

Simulating ISE and XPS designs in Active-HDL

Installing EDK Simulation Libraries in Active-HDL

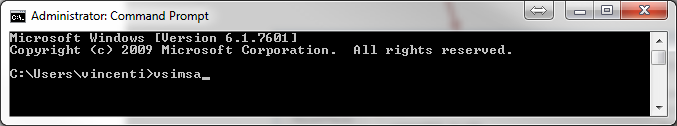

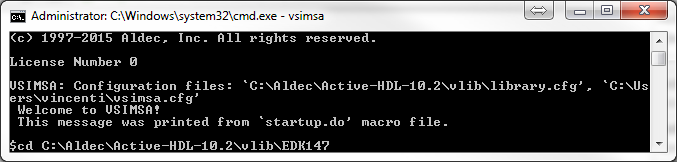

EDK Compilation scripts are designed to run in Active-HDL batch mode. To enter batch mode, open up the command prompt and run VSIMSA.

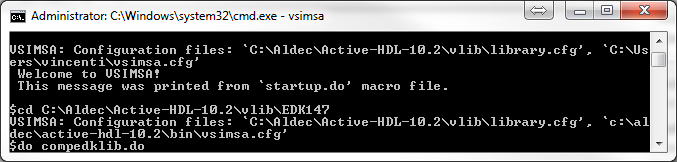

Change the present working directory to the location of the extracted library.

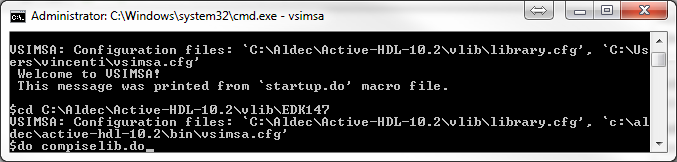

Run the scripts using the do command do compedklib.do

Note: Compilation of the EDK libraries require that the XilinxCore Libraries be installed. If this is not yet installed, compilation script will report an error. If the XilinxCore Libraries are not installed, they can be installed by running the compiselib.do script. To do this, simply use the do command do compiselib.do.

Set Active-HDL as the default simulator in ISE Project Navigator

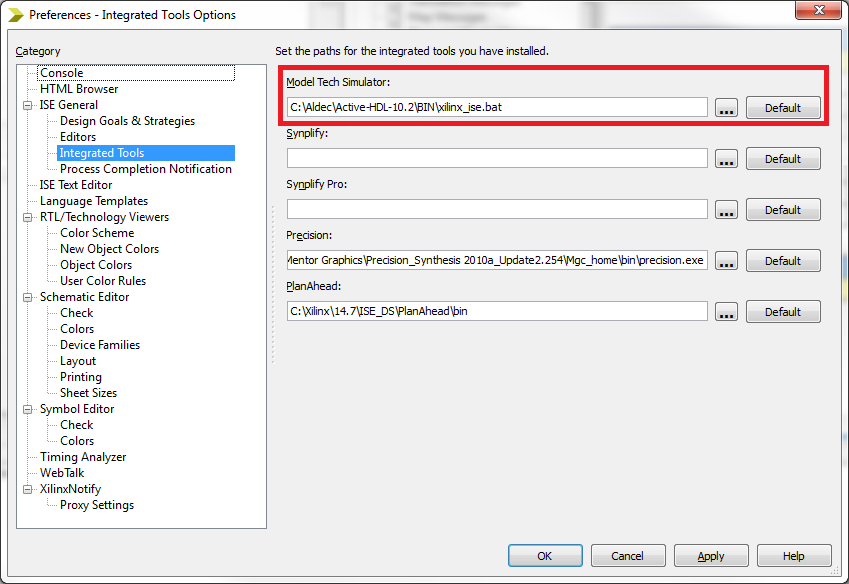

Go to ISE menu Edit | Preferences and select Integrated Tools under ISE General.

Click the browse button for the Model Tech Simulator and point to Aldec's file xilinx_ise.bat located in the Active-HDL\BIN (installation directory) folder.

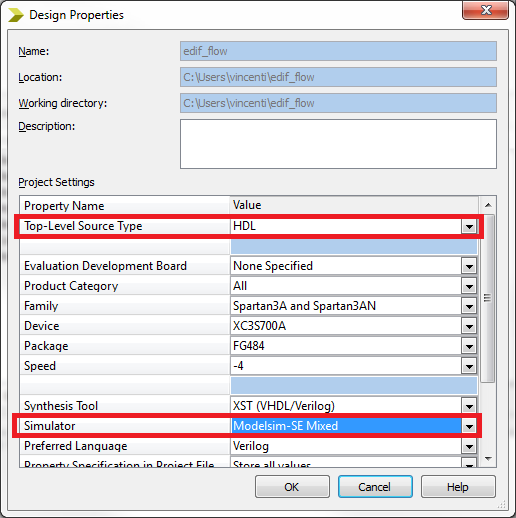

Go to ISE menu Project | Design Properties.

Select HDL option under Top-Level Source File and ‘Modelsim-SE’ Mixed option under Simulator.

Now, we need to set some advanced simulator properties.

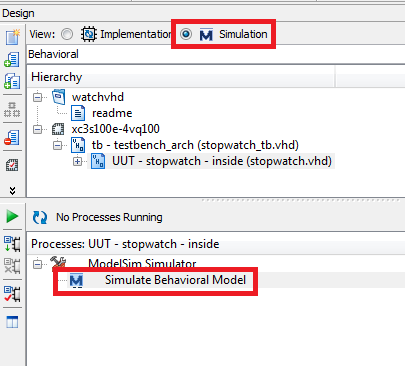

Make sure that Simulation view is selected in ISE Design tab. Then in the Processes tab you need to right click on Simulate Behavioral Model and select Process Properties.

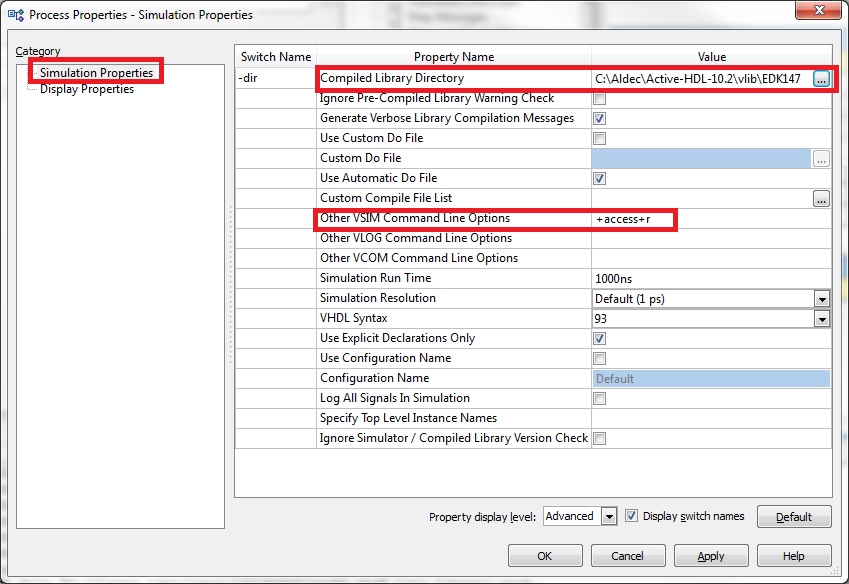

In Simulation Properties window, select Simulation Properties on the left and then enter +access +r under Other VSIM Command Line Options. This will allow you to trace your design signals later in the Active-HDL's waveform window.

In Compiled Library Directory option provide path to EDK library which you stored on your disk in above steps (Refer to Introduction)

Generating simulation files under ISE

Switch to Implementation view in Design tab of ISE and synthesize your design by running Synthesize-XST process. This is necessary even for behavioral simulation because some blocks such as MicroBlaze can only be simulated as a netlist in Active-HDL. Once the synthesis is over you will get several .ngc files in your design directory. Now we will have to generate an HDL simulation model from netlist for the MicroBlaze block.

Go to Windows OS Start menu and launch ISE Design Suite Command Prompt under All Programs | Xilinx ISE Design Suite | Accessories.

Change directory (with cd command) to your project directory where you have the ngc netlist file for MicroBlaze (e.g. microblaze_0_wrapper.ngc).

Type one of the following commands to generate simulation file for the processor core in either Verilog or VHDL format: For Verilog:

> netgen –intstyle ise –w –ofmt verilog –sim microblaze_0_wrapper.ngc microblaze_0_wrapper_netlist.v

For VHDL:

>netgen –intstyle ise –ar structure –w –ofmt vhdl –sim microblaze_0_wrapper.ngc microblaze_0_wrapper_netlist.vhd

Starting the simulation from ISE

Inside the ISE Design | Hierarchy window select set the View to Simulation.

Select your system top level entity in the Design window. After that you will be able to see Modelsim Simulator | Simulate Behavioral Model in the Processes window.

Right click on Simulate Behavioral Model and select Run. This will launch and start your simulation in Active-HDL.

Note: An Active-HDL project will be automatically generated with proper files added and the design compilation will automatically start in Active-HDL.

If you get errors in Active-HDL during compilation process you will need to either break the process of compilation in Active-HDL or wait till it is over and perform the following changes:

Open <XPS_project_name>.do macro file located in your main ISE project directory and replace the reference to microblaze_0_wrapper.vhd with the file that we generated above microblaze_0_wrapper_netlist.vhd (likewise for Verilog designs).

Remove ‘–novopt’ switch from all ‘vlog’ and ‘vcom’ commands located in <XPS_project_name>.do macro file

Remove ‘–novopt’ switch from ‘vsim’ command located in <ISE_design_name>.fdo macro file

Comment out ‘view signals’ command from <ISE_design_name>.fdo macro file

Rename <ISE_design_name>.fdo file to <ISE_design_name>.do and save it

Note: <XPS_project_name> means this file name depends on your XPS project name and <ISE_design_name> means this file name depends on top level file from ISE project. So depending upon these names script (macro) name can differ.

After that you can restart the process of compilation in Active-HDL. Right click on the *.do macro in Active-HDL's Design Browser and select Execute. When you run this macro multiple times you may see the following error message:

# Error: Cannot create mapping

It is safe to ignore these messages.

Upon successful execution of the .do macro your simulation will start and you will be able to observer your waveforms.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.