Simulink® Interface in Riviera-PRO

Introduction

The Simulink Interface built-into Riviera-PRO provides the integration of the Math Works' simulation tools with Aldec’s HDL-based simulation environment for FPGA and ASIC designs. The interface allows designers to co-simulate functional blocks described using mathematical formulas and VHDL entities, Verilog modules, EDIF cells, as well as SystemC modules that are used as black-boxes during the verification process performed within the Simulink environment.

Interface Specification

Software Requirements

MATLAB® 2011b or newer

Riviera-PRO2012.02 or newer

HDL Block Port Types

Regular HDL Black-Box: DOUBLE, SINGLE, Int8, uInt8, Int16, uInt16, Int32, uInt32, Fix and uFix up to 128 bits

Conversion Options

Port Cast for inputs: Signed (2's comp), Unsigned, Boolean

Port Cast for outputs: Signed (2's comp), Unsigned, Boolean, Int8, uInt8, Int16, uInt16, Int32, uInt32, Fix, uFix

Vector Width: Integer values between 1 and 256, the use of generics is allowed

Position of binary point (fractional part): unlimited

Quantization (HDL Black-Box inputs only): Truncate, Round

Overflow (HDL Black-Box inputs only): Saturate, Wrap, Error

Simulink Interface Setup

Step 1 Run Riviera-PRO Setup Program

Follow procedures described below for setting up the Simulink Co-Sim interface:

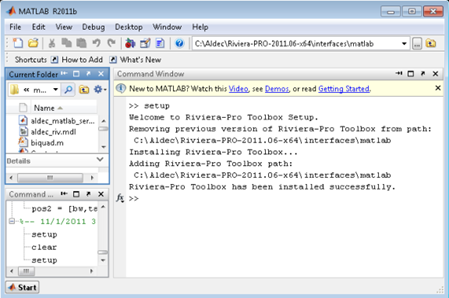

Start MATLAB.

Change the Current Directory in the MATLAB window to the $ALDEC\interfaces\matlab directory.

Enter the setup command in the MATLAB Command Window and press Enter. The appearing warning dialog box prevents you from accidental removing previous versions of the Riviera-PRO Blockset installed in MATLAB.

Press Yes to continue. The following message should be displayed in the Command Window

Figure 1 Running Setup

After the setup is finished, you are able to use Riviera-PRO Blockset immediately. If the Simulink Library Browser or Help window is already open, you may need to restart MATLAB in order the changes to take effect.

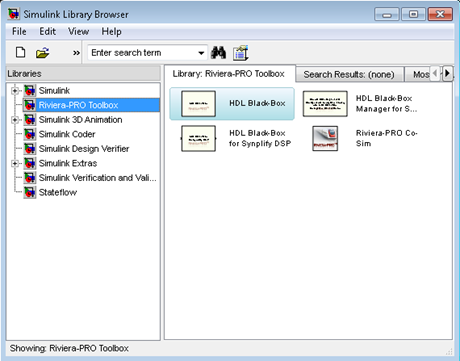

When you run the Simulink Library Browser by typing simulink in Command Window or clicking on the Simulink toolbar button, you will see the Riviera-PRO Blockset in the left pane.

Figure 2 Simulink Library Browser

Note: If you run into problems running setup due to rare platform-specific issues, you will need to set up the interface manually. Please refer to the Riviera-PRO User's Guide for detailed instructions.

Step 2 (Optional): Updating Existing Diagrams

After installing a new version of the Riviera-PRO Blockset, blocks coming from previous versions of Riviera-PRO Blockset must be updated. The riv_UpdateModel function is provided to automate the update process. You can use the command without arguments to update the currently open model or you can specify the model to be updated by using command such as riv_UpdateModel(‘ model_name’).

Step 3 (Optional): Getting information about Riviera-PRO Blockset

Generating Block Description File for Simulink Interface

Before an HDL unit can be co-simulated, an interface description file (M-file) for that unit needs to be generated. The file describing an interface of a VHDL entity/architecture pair, a Verilog module, or EDIF cell (*.m) can be generated by using the Riviera-PRO GUI or command line.

Generate the M-file in Riviera-PRO

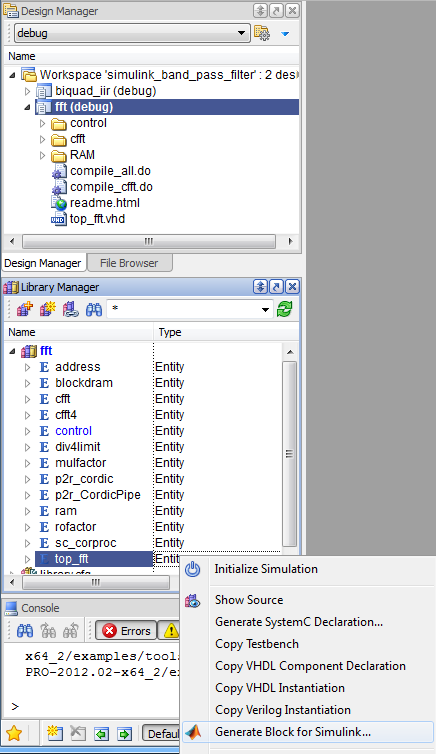

Open a workspace and set an active design that contains units to be co-simulated. Note: Using workspace and designs is not obligatory but it is strongly recommended as it provides better design management.

Compile your source files that describe the design unit that be used as a black-box in Simulink

Select the library units in the Library Manager, right-click on this unit, and select the Generate Block for Simulink option from the pop-up menu.

Figure 3 Library Manager

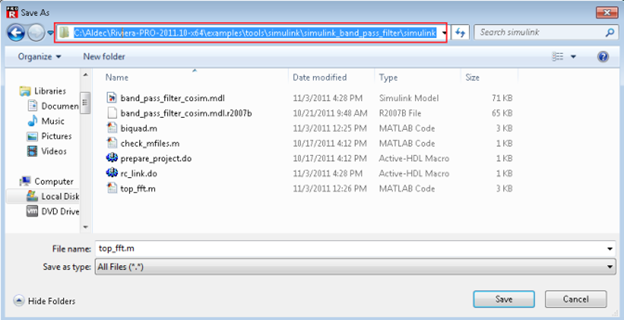

The Generate Block for Simulink dialog box will open. Verify the location of the generated blockset descirption file and press Save to close the window.

Figure 4 Generating Block for Simulink

Alternatively, you can generate the M-file from the command line using the simulinkgenmod command in the Console.

simulinkgenmod -overwrite -o $dsn/../Simulink/top_fft.m top_fft

NOTE: If you would like to simulate several HDL entities on the Simulink’s diagram you will have to generate Block Description, i.e. the .m file, for each of the entity/architecture pair. When you run the Co-Simulation for Simulink, make sure to specify the same path in the Output Directory field for every HDL component you will simulate in MATLAB Simulink.

Using Rivier-PRO Blockset blocks in Simulink Diagram

Before you can run co-simulation in Simulink, you need to instantiate blocks available in the Riviera-PRO Toolbox in a Simulink model window. You may also want to modify their parameters.

Switch to MATLAB. Change the current directory and set it to the location of the simulink/ directory storing the library of black-boxes created in Riviera-PRO (in the Generate Block for Simulink dialog box).

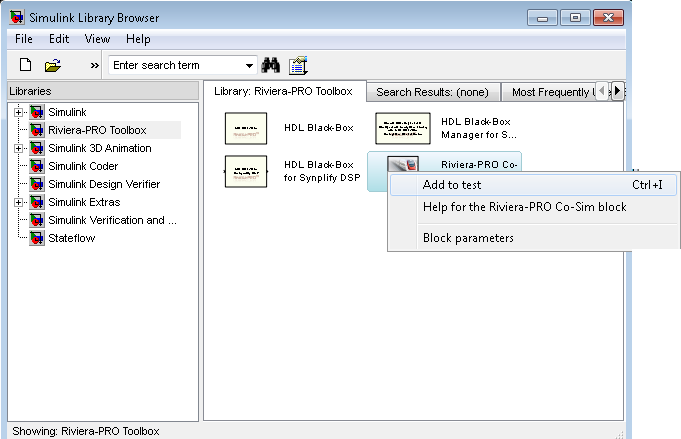

Click the Simulink icon from MATLAB main toolbar or type simulink in the MATLAB Command Window to open the Simulink Library Browser window.

In the left pane of the Simulink Library Browser window, the Riviera-PRO Blockset is displayed. The contents of the blockset are displayed in the right pane. This version of the blockset contains the following blocks:

Riviera-PRO Co-Sim

HDL Black-Box

HDL Black-Box Manager for System Generator 8.x

HDL Black-Box for Synplify DSP

To add the Riviera-PRO Co-Sim block to the Model window use the Add to the current model command or drag-and-drop.

Figure 5 Simulink Library Browser: Adding to model

Select HDL Black-Box and add it to the same Simulink model window. A Select HDL Black-Box Configuration dialog box should pop-up after you dragged-and-dropped the block template from the Simulink Library Browser window into the model window. There, please specify the functionality and associate an HDL model which was generated before (block description file- .m) by selecting the black-box configuration file.

By Using HDL-Black-Box Parameter window you can control some of the Riviera-PRO features for waveform, stimulus and breakpoint etc.

Configure Timing Dependencies between Riviera-Pro and Simulink

One of the most important issues for co-simulation between two simulators is the time-domain synchronization of the two simulation runs. Following aspects must be properly considered in order to successfully configure the co-simulation:

relation of time-domains between simulators

relations of sampling period between ports of all HDL Black-Boxes instantiated in the Simulink model

configuration of clock ports of HDL Black-Boxes

The Riviera-PRO Toolbox provides all features required to flexibly handle the synchronization of the simulators and time parameters of the ports of the HDL Black-Boxes in both simulators. Those timing related dependencies are set either in the Riviera-Pro Co-Sim block or HDL Black-Box parameter dialog box. You can set the following important timing related dependencies:

Configuring the Relation of Time-domains between Simulators

Selecting the Reference Period

Configuring Sampling Period of the HDL Black-Box Ports

Configuring Clock Ports of HDL Black-Boxes

Using Optional Synchronization Signals

Riviera-PRO Co-Sim Dialog Box

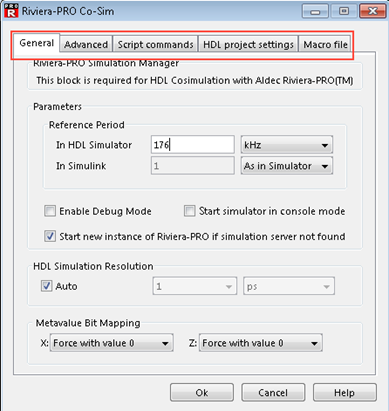

Double-click the Riviera-PRO Co-Sim block to open the Riviera-Pro Co-Sim dialog box. It allows you to configure the sampling period and the relationship between Riviera-PRO and Simulink time domains as well as general co-simulation settings.

Specify new settings and apply the changes clicking the OK button. This dialog box provides different settings necessary for pre-initialization and post-initialization as well. You may use the following tabs of Co-Sim dialog box to configure the co-simulation parameters:

General tab:

Parameter Reference Period defines relationship between Riviera-PRO and Simulink time domains and specifies a base sampling rate for all HDL black-boxes. In the figure Reference period for HDL simulator is given 176 kHz frequency so in case of frequency unit resulting sampling period is calculated as reciprocal of entered value.

You can set Enable Debug Mode which will run co-simulation in a special diagnostic mode. In this mode, the simulation is stopped after the design has been initialized, which then allows you to set breakpoints, watch selected signals, and trace HDL source code inside Riviera-PRO.

You can set Start simulation in console mode. You can set HDL simulation resolution.

You can decide mapping of Metavalue.

NOTE: Be aware of the round-off error when specifying a period by using frequency units. The fractional part of the resulting period will be rounded to three digits. All parameters specifying the time are defined as integers related to the Reference Period.

Figure 6.1 Riviera-PRO Co-Sim Dialog Box (General Tab)

Advanced tab: It allows you to give waveform file name in which co-simulation results will be displayed. It also allows you to save test vectors for HDL part of you Simulink design for both driving values as well as response value so later you can use this file for standalone simulation without use of the Simulink.

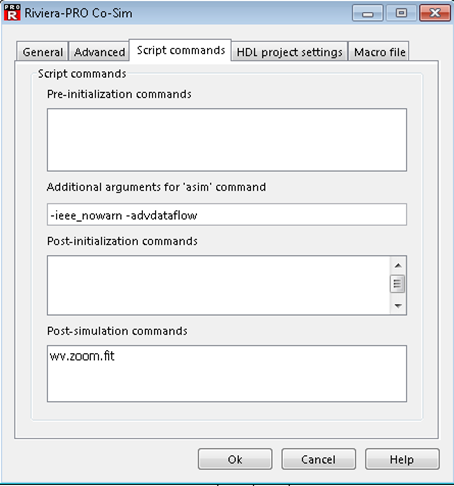

Script Commands tab: (as shown in Fig 6.2) it allows you to set pre / post –initialization commands and post simulation commands. You can set different arguments (switches) for asim command also. In figure below we have mentioned some asim switches like no ieee warning and enable advanced dataflow. You can set Post-initialization commands like enabling code different coverage etc. You can have different waveform related commands in Post-simulation commands like we have here for zoom to fit current view.

Figure 6.2 Riviera-PRO Co-Sim Dialog Box (Script commands)

HDL Project Settings tab: You can set ‘use following HDL workspace / files’ for co-simulation. Simulator path can be set here as well.

Macro file tab:

Use macro enables specifying a macro file to be executed in Riviera-PRO before the co-simulation run. Here you can set different compilation options you want to have in your design compilation like debug, incremental options (switches) etc.

Use macro typed below enables specifying in the text box below a set of commands to be executed in Riviera-PRO during compilation time.

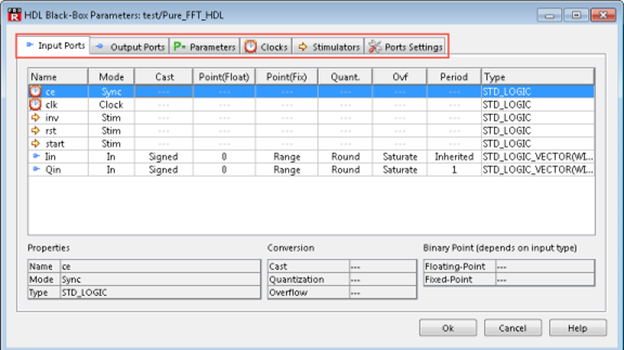

Specifying HDL Black-Box Parameters

Double-click on a Black-Box (VHDL model) symbol for what you want to edit the configuration. The HDL Black-Box Parameters dialog box opens. The dialog box provides a set of block-specific options (depended on block type) that have been grouped in the following categories:

Input and Output Ports: Lists all objects that will be simulated and/or observed during co-simulation.

Mode: Shows the direction of data transfer or a mode for special signals. The Stim mode indicates that a signal has been added to the Stimulators tab, Clock and Sync indicate that signals have been added to the Clocks tab.

Period: This column is important. It defines the update rate for input and output. As shown in figure 7.1 below sampling period is set to 1 this means that data between Simulink and HDL blocks will be exchanged in time intervals equal to the Reference Period (set in Co-Sim block – 176 kHz). For example if Period is set to 2 then rate of update will be reference period divided by 2 (88 KHz).

Point: Allows specifying the binary point for a vector. As HDL Black-Box accepts input data of both floating- and fixed-point types, two separate options are provided:

Point (Float) - double numbers in Simulink are converted to binary numbers in fractional two's complement notation. This parameter defines position of the 2^0 bit.

Point (Fix) - the point value can be inherited from an input fixed-point number (by setting Range or Accuracy) or customized independently (value set for float-point types can be used by setting As for Float value).

Parameters: Displays port generics/parameters defined in a black-box interface; if necessary, an actual value of a generic/parameter can be modified. See Parameters for details.

Figure 7.1 HDL Black-Box Parameters (Input Ports Tab)

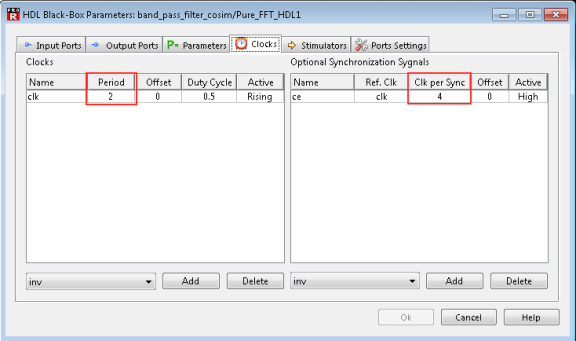

Clocks: (as shown in Fig 7.2) allows precise specification of model synchronization signals such as Clock, Clock Enable, or other synchronization signals. For different operating frequency entities, the sampling period can be accomplished in two ways: by using one clock frequency for all HDL Black-Boxes and additional synchronization signals to activate block, or by using multiple clock frequencies directly. Clock period here is product of reference period and integer value given in ‘Period’ column. In optional synchronization signals we have enable (‘ce’) signal which can be used to activate one HDL black box slower than the other HDL black box.

Settings for the clk port selected as the Clock signal:

Period: 2 - forces clk period of 11.36us (it corresponds to 88 kHz, It divides reference period by integer number given here)

Settings for the ce port selected as the Sync signal:

Reference Clock: clk - uses clk Clock as reference

Clk per Sync: 4 - activates the ce port during every 4th clk period, which results in the block activation period of 45.45us (it corresponds to 22 kHz)

Figure 7.2 HDL Black-Box Parameters (Clocks Tab)

Stimulators: Allows entering user-defined formulas (in the format compatible with the ‘force’ command in HDL simulators) and defining stimuli for inputs that have not been selected in the Clocks tab.

Port Settings: It allows you to select ports you want to be in waveform by clicking inside Wave column and can customize signal properties (e.g. radix, notation) for each port. Here you can set signal breakpoints too by double clicking in ‘Break column’.

Once you are done specifying HDL Black-Box Parameters click Ok.

Note: You have to follow same steps to customize HDL black-box parameters in another component (biquad_iir) before you proceed to next step.

Running Co-simulation

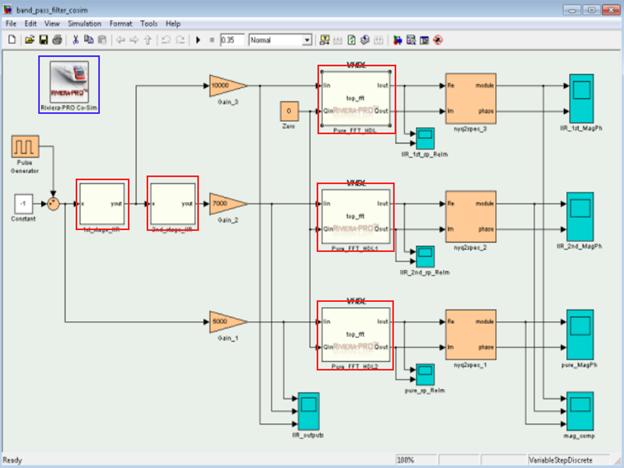

Now you can complete Simulink diagram by connecting different HDL Black-Boxes to other Simulink components as per you design requirements as shown in Figure 9.

Preparing Riviera-PRO for co-simulation

In order to set Riviera-PRO as an HDL simulation server, it needs to be switched to the simulation server mode. By default, Riviera-PRO is not working as the simulation server. There are two approaches of setting up Riviera-PRO as the simulation server:

One of existing instances of Riviera-PRO is switched to the simulation server mode and used for all co-simulation sessions.

A new instance of Riviera-PRO is started automatically during the first simulation and reused for subsequent sessions.

If an instance of Riviera-PRO is already running, you can switch it to the server mode by issuing the following command in the Console window: rc.open -xml -socket <port_number>

When Riviera-PRO is set as an HDL simulation server It starts responding to commands issued by Simulink, i.e. acts as the simulation server for Simulink.

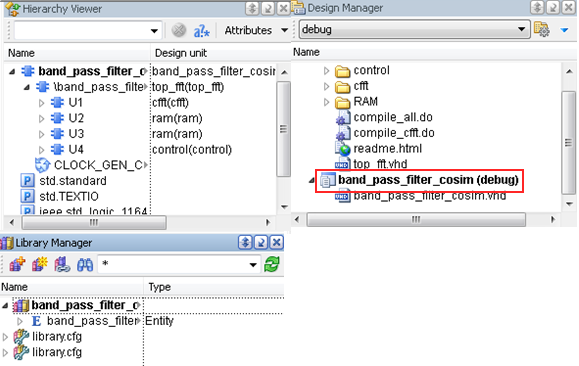

Starting co-simulation

In order to start simulating your model, choose the Start command from the Simulation menu of the Simulink model window or click the Start simulation toolbar button. When you initiate co-simulation in the Simulink environment, a new design (band_pass_filter_cosim) is created and added to the workspace (matlab_cosim). Riviera-PRO loads the new workspace. Previously, the workspace contained designs that were used to generate block description files (*.m). The workspace along with the automatically generated matlab_cosim workspace is presented in Figure 8.

Figure 8 automatically generated matlab_cosim workspace containing the band_pass_filter_cosim design

The $wsp/band_pass_filter_cosim design contains automatically generated wrapper that binds all HDL components/modules required to co-simulate HDL black-boxes instantiated in the Simulink model that is shown in Figure 9. In the figure 9 boxes in red are VHDL-models (black boxes for Simulink) generated in Riviera-PRO and box in blue is interface module which handles all the parameter details regarding interface. Remaining modules are native Simulink modules.

Figure 9 example model window

When the workspace is generated and the co-simulation has been initialized, the design is compiled and, in the next step, the HDL simulation session is run. The entire process is executed and based on commands passed by Simulink to Riviera-PRO through the co-simulation interface. The commands execution can be monitored in the Console window:

#workspace.design.create {band_pass_filter_cosim} {C:\Aldec\Riviera-PRO\examples\tools\simulink\simulink_band_pass_filter\simulink\mlab_cosim} # workspace.design.setactive {band_pass_filter_cosim} ... <compilation commands> ... # asim <options> ... # ELBREAD: Elaboration process. # KERNEL: Main thread initiated. ... # ELAB2: Elaboration final pass... # ELAB2: Create instances ... # KERNEL: PLI/VHPI kernel's engine initialization done. # PLI: Loading library 'C:\Aldec\Riviera-PRO\bin\systf.dll' # VHPI: Loading library 'C:\Aldec\Riviera-PRO\interfaces\simulink\riv_simulink_pipe.dll' # VHPI: Interprocess communication system loaded. # ELAB2: Create instances complete. ... # KERNEL: Kernel process initialization done.Note:

Each co-simulated unit requires one Riviera-PRO Co-Sim block to be added to the Simulink model window.

The name of the block description file cannot be the same as the name of a Simulink function. See "Functions - By Category" in the Simulink documentation for a complete list of functions.

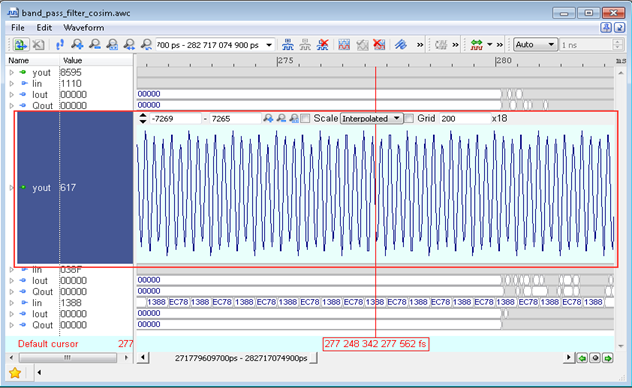

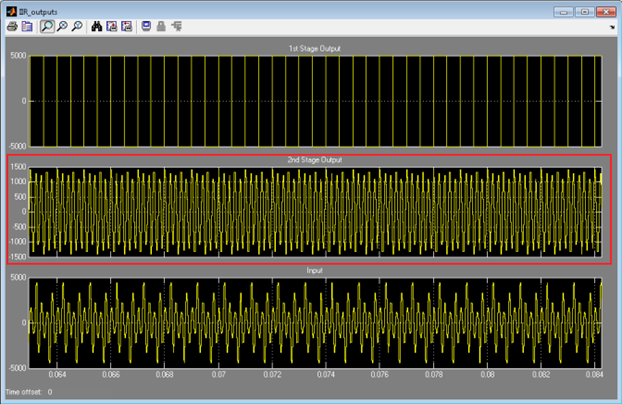

Simulation Results

Once simulation is ended Riviera-PRO waveform window gets populated with different wave form.

You can convert waveform display of signals to analog display and compare these waveforms with the Simulink generated waveforms and analyze your results.

Converting waveform display for particular signal to analog display can be done in two ways:

Select the signal in waveform and right click Properties | Display tab and select analog.

Write wave command in post simulation commands text box of Riviera-PRO Co-Sim block inside Simulink as describe in ‘Riviera-PRO Co-Sim Block’ section of this training tutorial (Figure 7.2) wave -height 200 -analog -analog-interpolated {/Hierarchy path/\yout}

You can observe results like shown in figures below. Red highlighted waveforms in both the figures are of same signal ‘yout’

Figure 10 Riviera-PRO Waveform

Figure 11 MATLAB Waveform

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.