Co-Simulation with QEMU and Riviera-PRO

Today’s SoC FPGAs present new verification challenges for system, software, and hardware engineers. Common issues related to HW/SW integration continue to increase, and yet many companies are still running system validation in the testbed. Finding issues in the testbed is often too late and can cause project delays. Simulation has been the de-facto functional verification technique for semiconductors for many years because of its ease-of-use and advanced debugging capabilities. As FPGA architectures transform into SoC architectures with multi-cores, operating system, software/drivers and programmable logic, the need for a system level simulation has never been more crucial.

To meet various user requirements and environments, Aldec provides a couple of options for Zynq 7000 and Zynq MPSoC system HW/SW co-simulation between QEMU and Riviera-PRO:

- Using LibSystemCTLM-SoC library via Remote Port IPC

- Using Aldec QEMU Bridge and AXI BFM

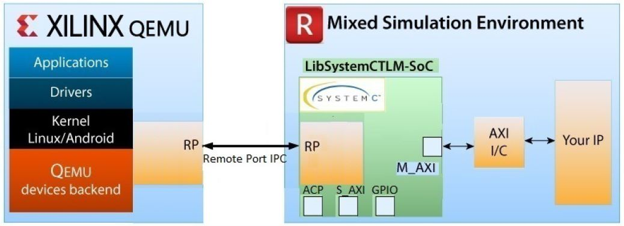

Co-Simulation Using LibSystemCTLM-SoC library via Remote Port IPC

System integration and co-simulation of HDL code, with software applications/drivers executing in QEMU, are now simplified with a full compilation of SystemC to library (LibSysytemCTLM-SoC), executed with Riviera-PRO HDL simulator. The LibSysytemCTLM-SoC utilizes the Remote Port to connect both Riviera-PRO and QEMU, and it converts SystemC TLM transactions to AXI, and vice versa, providing a fast interface for co-simulation.

Figure 1: Using LibSystemCTLM-SoC library via Remote Port IPC

- The combination of Riviera-PRO, Xilinx libSystemCTLM-SoC library and Xilinx QEMU supports the entire PS verification with IRQ

- No need to use additional elements like BFM, TLM or bridges

- QEMU and Riviera-PRO communication is integrated in the form of a library

- No need for manual changes to support system integration

The LibSysytemCTLM-SoC library supports the Remote Protocol with Transfer Level Modeling (TLM). This transaction-accurate interface enables the full SoC co-simulation between the Programmable Logic (PL) system and Processing System (PS).

The system co-solution divides the system into two parts. The PS is emulated in QEMU, and PL is simulated in simulator Riviera-PRO. All the traffic and synchronization data are supported by the library. All the PS transaction interfaces are verifiable such as AXI, GPIO and HP. For more information about using transactions in Riviera-PRO, refer to documentation Riviera-PRO Transactions. The LibSysytemCTLM-SoC library recorder is responsible for logging the PS interface into ASDB (Aldec Simulation Database) format.

Hardware engineers (using Riviera-PRO) can set break points in the HDL code, examine data flow, and even analyze the code coverage and paths that are exercised by the software application running in QEMU. Software engineers (using QEMU) can use GNU Debugger (GDB) to instrument both the kernel and the driver to step through the code using breakpoints.

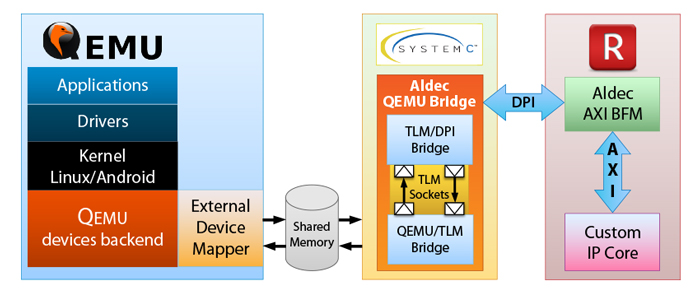

Co-simulation using Aldec QEMU Bridge and AXI BFM

There is another way to do co-simulation which requires Aldec QEMU bridge and AXI BFM. The QEMU bridge provides the communication between PS (QEMU) and PL side, and users can simulate the AXI-based transactions using the AXI BFM.

The QEMU Bridge connects Riviera-PRO and QEMU and converts SystemC TLM transactions to AXI and vice versa providing a fast interface for co-simulation.

Figure 2: Using Aldec QEMU Bridge and AXI BFM

The AXI Bus Functional Models (BFMs) developed by Aldec for RTL simulation of AXI-based designs is available in Riviera-PRO. The BFMs are delivered as encrypted Verilog and System Verilog modules. User test bench can test the BFMs via Verilog or System Verilog tasks API provided by Aldec. Here are some of the BFMs supported by the Aldec AXI BFM: AXI 3 Master, AXI 3 Slave, AXI 4 Master, AXI 4 Slave, AXI 4 Lite Master, AXI 4 Lite Slave, AXI 4 Stream Master, AXI 4 Stream Slave.

Each BFM enables users to turn on built-in AXI transaction recorder for logging AXI transactions into ASDB (Aldec Simulation Database) format. For more information about using transactions in Riviera-PRO, refer to documentation Riviera-PRO Transactions.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.