COVID-19 Detection

FPGA-based lung infection (pneumonia) detection for Covid-19

Covid-19 has made 2020 an unforgettable year for everyone around the world. Many people got infected and many lost their loved ones.

There have been many safety rules suggested by the World Health Organization (WHO) to protect people against the virus. Also, great emphasis has been placed on the importance of early recognition of Covid-19 symptoms and – if a person is becoming very unwell – detecting the virus’ effect on the patient’s body; and especially their lungs.

One of the most accurate methods of assessing lung damage is the chest x-ray. However, because of the high number of patients around the world, fast and high-performance detection methods are crucial.

In this respect, neural networks can help physicians detect pneumonia, which is infection in both lungs, in the early stages of the disease.

While neural networks can be implemented using a number of different processing techniques, FPGAs are the best option because of their high performance and reconfigurability.

Because of the demand for lung infection detection, Aldec has prepared an FPGA based Covid-19 diagnostic solution which works with TySOM embedded development board. Neural network algorithms are computed by Zynq MPSoC XCZU19EG on TySOM-3A-ZU19EG devices.

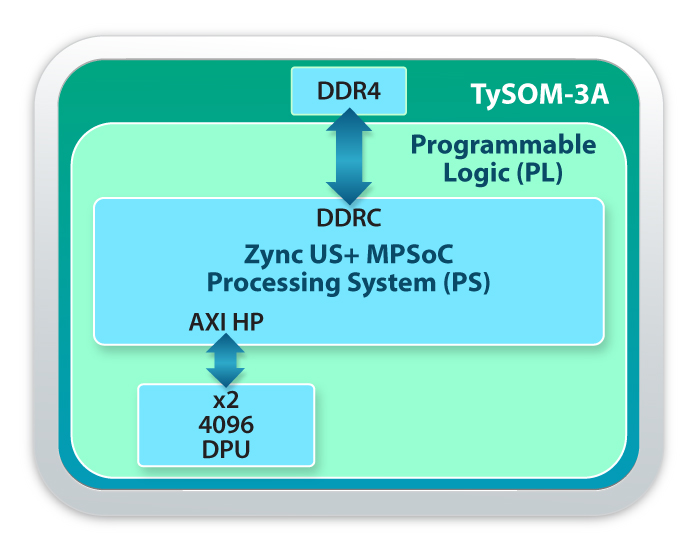

To detect Covid-19 (Coronavirus) infection in the lungs using deep learning on FPGA, a dataset including 3575 pictures have been used for training and 136 pictures for algorithm validation. Images in the dataset have been divided into two groups: patients with pneumonia patients without. The deep learning algorithm will classify the pictures into COVID-19 infected and non-infected. Yolov3 neural network has been used in this project. The result is sent out of the board using the Wi-Fi device on the board. There are 2x Deep learning Processing Units (DPU) used inside the FPGA for this project. Following image shows an overview of the design layout.

Here is a summary of running Covid-19 (Coronavirus) detection on FPGA using deep learning:

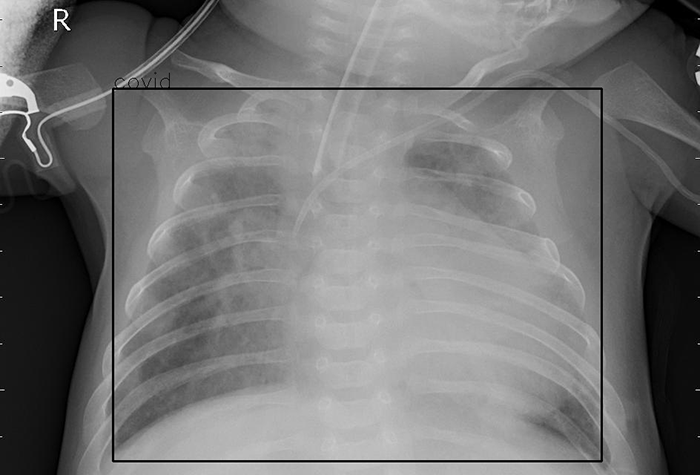

- Probability of Covid object detection 99.97%

Figure 1 Result of Covid-19 infection detection using FPGA

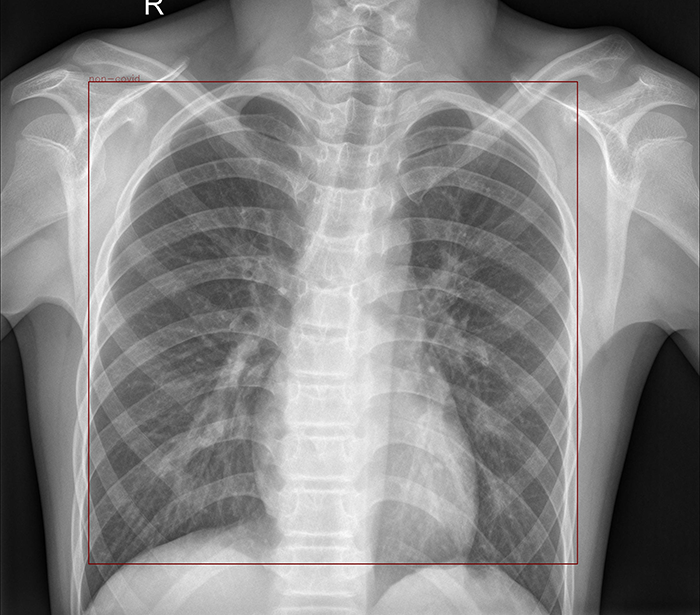

- Probability of non-Covid object detection 99.71%

Figure 2 Result of TySOM-3A non-covid object classification

After running some benchmark for this project, the following results have been achieved:

- Used programmable logic of Zynq MPSoC US+ ZU19EG chip:

| Part | LUT | LUTRAM | FF | BRAM | DSP | IO | GT | BUFG | MMCM |

| Utilization (%) | 29.7 | 9.9 | 26.6 | 58.5 | 60.2 | 8.8 | 18.7 | 2.3 | 27.2 |

- Frame Per Second summary

| Number of DPU cores | Application | Yolov3-Custom | Yolov3-Example |

| 2 | FPS | 28.1 | 27.6 |

- DPU clocking setup

| DPU Instance Name | dpu_xrt_top_1 | dpu_xrt_top_2 | |||||||

| DPU Clk | Aclk | Ap_clk_2 | Aclk | Ap_clk_2 | |||||

| Clk Frequency (Hz) | 300 | 600 | 300 | 600 | |||||

Aldec has provided this solution to help save lives. Users of TySOM board can access this reference design and expand to add more features to it. Below you can find this solution content.

Main Features

- Includes TySOM-3A-ZU19EG embedded development board

- Include reference design on how to run the demo

- Up to 30 FPS performance on lung infection detection

- Prebuilt and ready to use files pre-loaded into the SD card

Solution Content

- FPGA-Based COVID-19 lung infection detection using deep learning

- TySOM-3A-ZU19EG Vitis platform

- Prebuilt petalinux embedded OS to run on the board

- Includes instruction and the source code for the design

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.