HES-XCVU9P-ZU7EV

Capacity

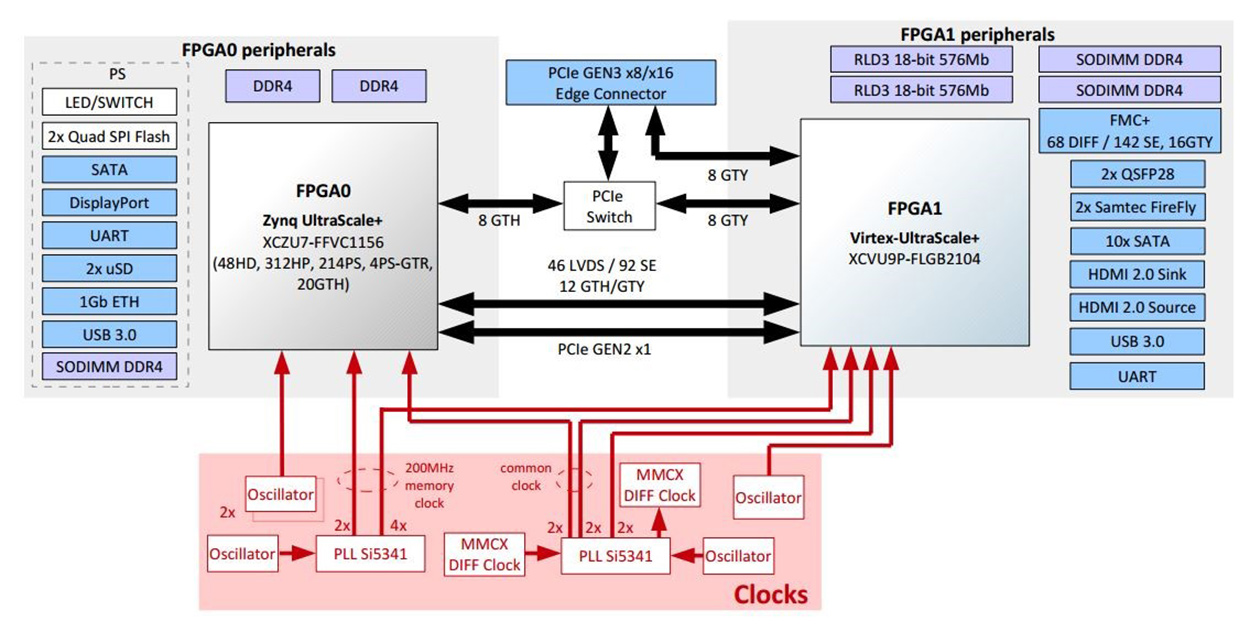

The HES-XCVU9P-ZU7EV is designed for High-Performance Computing (HPC) applications which require immense digital signal processing. The board features a unique integration of a ZU7EV Zynq® UltraScale+™ MPSoC and a VU9P Virtex® UltraScale+™ FPGA. This heterogeneous computing platform leverages a Quad-core ARM® Cortex-A53, Dual-core ARM® Cortex-R5 real-time processing units, an ARM® Mali-400 MP2 GPU, integrated H.264/H.265 video codec, and UltraScale+™ programmable logic in a 16nm FinFET node.

Available onboard external memory resources include three (3) DDR4 SODIMM slots and two (2) modules of 576Mb RLDRAM-3 (1Gb total). On-chip memory for the Zynq® programmable logic includes 11Mb of Block RAM and 27Mb of UltraRAM. On-chip memory for the VU9P programmable logic includes 75.9Mb of Block RAM and 270Mb of UltraRAM.

| Resources | VU9P Virtex UltraScale+™ FPGA | ZU7EV Zynq UltraScale+™ MPSoC |

|

Logic Cells/LUTs (K) |

2586 | 504 |

|

Total Block RAM (Mb) |

75.9 | 11 |

|

UltraRAM (Mb) |

270 | 27 |

|

DSP Slices |

6840 | 1728 |

|

Transceivers |

76 GTY 32.75 Gb/s | 20 GTH 16.3Gb/s |

|

I/O |

702 HP | 214 PS, 312 HP, 48 HD |

Clocking

Clocking is provided by oscillators, PLLs, and MMCX connectors. Dedicated oscillators are connected directly to the FPGA devices as well as onboard PLLs. The onboard PLLs provide any-frequency common clocks for both FPGA devices and dedicated any-frequency clocks to the VU9P to accommodate a variety of applications. Clocking can also be provided through the FMC+ connector through thirteen (13) differential clock inputs to the VU9P.

Hosting & Interfaces

The board is connected to a workstation or server through the board’s PCIe x16 edge connector. A wide variety of interfaces are available to be connected to the FPGA devices.

| Interfaces | |

| VU9P Virtex® UltraScale+™ FPGA | ZU7EV Zynq® UltraScale+™ MPSoC (connected to the ARM® processing system) |

|

|

Aldec provides the Hes.Asic.Proto software package with necessary drivers and utilities for programming and communication with the board. For quick bring-up of host connection, Aldec provides ready to use image of the embedded Linux for ZU7EV device and HES Proto-AXI solution, which consists of a bridge module IP with AMBA AXI interface and accompanying PCI Express HES driver with C++ API for Linux and Windows PC allowing to transfer data directly to the AMBA AXI local bus behind the bridge. Power is supplied by a standard 6-pin PCIe power cable.

HES-XCVU9P-ZU7EV

FPGA & Capacity

- Main FPGA: Virtex UltraScale+ XCVU9P-FLGB2104 (I/O: 702 HP, 76 GTY)

- Host FPGA: Zynq UltraScale+ XCZU7EV-FFVC1156 (I/O: 214 PS, 48 HD, 312 HP, 20 GTH)

Flexible Clocking

- Two (2) dedicated any-frequency clocks to VU9P

- Two (2) common any-frequency clocks to VU9P and ZU7EV

- Dedicated oscillators for VU9P and ZU7EV

- Thirteen (13) differential clock inputs from FMC+ to VU9P

Memory Resources

- Memories connected to the VU9P

- 2x 18-bit 576 Mb RLDRAM-3 modules (1Gb total)

- 2x SODIMM DDR4 slots

- Memories connected to the ZU7EV

- 2x 4Gb DDR4 modules (8Gb total)

- 1x SODIMM DDR4 slot

- 2x 512Mb Quad SPI Flash (1Gb total)

Interfaces & Hosting

- Host interfaces connected to ZU7EV

- PCIe 3.0 x8

- SATA

- DisplayPort

- UART

- 2x MicroSD

- 1Gb Ethernet

- USB 3.0

- Host interfaces connected to VU9P

- PCIe 3.0 x8/x16

- FMC+ (68 DIFF / 142 SE, 16 GTY)

- 2x QSFP28

- 2x Samtec Firefly

- 10x SATA (8x HOST and 2x DEVICE)

- HDMI 2.0 Sink

- HDMI 2.0 Source

- USB 3.0

- UART

- Hosting

- Aldec HES Proto-AXI drivers and programming utilities

Miscellaneous

- USB 3.0, uSD card socket and QSPI Flash memory for configuration

- 2x 4Gb DDR4 and DDR4 SO-DIMM socket for control FPGA

- DisplayPort connected to control FPGA

- SATA connected to control FPGA

- 1Gb Ethernet connected to control FPGA

- UART interface connected to control FPGA

- Power supply voltages supervisor

Software Support

- Full integration with Aldec HES/DVM

- Full support for Xilinx Chipscope debug and embedded logic analyzers via JTAG

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2025 Aldec, Inc.