Living on the Edge

by Farhad Fallahlalehzari, Applications Engineer, Aldec

As the deployment of Industrial IoT systems continues to proliferate, the streams of data transferred to the cloud skyrockets, drastically increasing the cost for cloud computing.

To solve this, many systems designers are adopting edge computing, in which data processing is done close to the source (e.g. sensors) in a bid to reduce data transfer, storage and processing costs, plus address a few other concerns over Cloud Computing, in particular security.

Big Data is a broad label for the growing amount of data generated by IoT devices and smart systems. For instance, some aircraft engines have more than 5,000 elements that are monitored at relatively high sample rates. Most of the data is transferred to a ground station for the real-time monitoring of the engine and for future R&D work. But this is only part of a growing trend. Most ‘smart’ systems produce vast amounts of data which needs to be processed immediately or be stored for subsequent processing

To store Big Data, huge datacentres are required. These are often costly, need a spacious climate-controlled environment and require regular maintenance. The alternative is Cloud Computing, the on-demand delivery of compute power, applications and other IT resources, and cloud providers - such as Amazon with its web service (AWS) - provide a simple way to access their servers, databases, processing and platforms and storage devices

For the rest of this article, please visit New Electronics.

Hardware and software engineers designing SoC FPGAs stand to profit from Aldec QEMU Bridge

Aldec supports an integrated co-simulation environment with virtual processor emulator

Henderson, NV – November 15th, 2017 – Aldec, Inc., an industry leader in Electronic Design Verification, has added QEMU Bridge to the latest release of Riviera-PRO™, the company’s advanced verification platform, to enable hardware/software co-simulation of designs intended to run on SoC FPGAs.

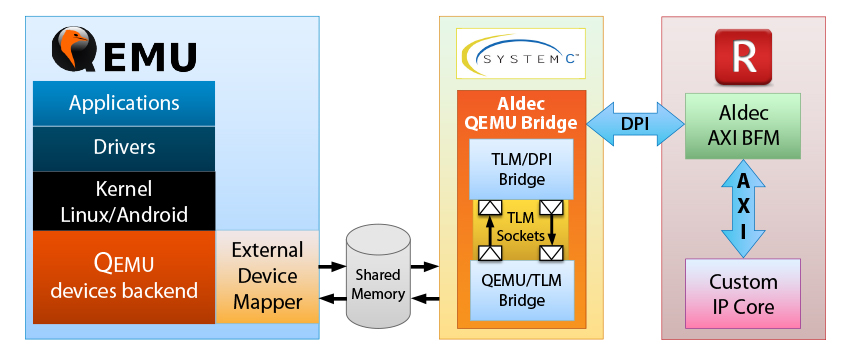

Integration and simulation of FPGA custom IPs with software applications and drivers executing on the virtual processor in QEMU is now possible and simplified. The QEMU Bridge converts SystemC TLM transactions to AXI and vice versa providing a fast interface for co-simulation.

“System integration is becoming increasingly challenging in light of growing design sizes and device complexity,” Radek Nawrot, Software Product Manager. “The co-simulation activities facilitated through QEMU Bridge enables hardware and software engineers to work together to locate, identify, and retire bugs at an earlier stage in the development cycle, thus saving both development time and costs.”

Hardware engineers (using Riviera-PRO) can set break points in the HDL, examine data flow, and even analyze the code coverage and paths that are exercised by the software application running in QEMU. Software engineers (using QEMU) can use GNU Debugger (GDB) to instrument both the kernel and the driver to step through the code using breakpoints.

For a demonstration video of the solution, go to HDL and Software Co-Simulation with QEMU and Riviera-PRO.

Also new to Riviera-PRO 2017.10:

- Significantly improved performance when using code containing many inline randomized calls

- Simulation speed of UVM design is up to 29% faster

- VHPI design simulation speedup

- Direct interface with ALINT-PRO™ Design Rule Checking tool

- Mixed-Signal Silvaco® SmartSpice™ Interface (initial stage)

- Pre-compiled Aldec AXI BFM 1.7

- Histogram can now be created in the Plot window

For additional information, tutorials, Overview Presentation and What’s New, and free evaluation downloads, visit http://www.aldec.com/Products/Riviera-PRO.

About Riviera-PRO

Riviera-PRO™ addresses verification needs of engineers crafting tomorrow’s cutting-edge FPGA and SoC devices. Riviera-PRO enables the ultimate testbench productivity, reusability, and automation by combining the high-performance simulation engine, advanced debugging capabilities at different levels of abstraction, and support for the latest Language and Verification Library Standards.

About Aldec

Established in 1984, Aldec is an industry leader in Electronic Design Verification and offers a patented technology suite including: RTL Design, RTL Simulators, Hardware-Assisted Verification, SoC and ASIC Prototyping, Design Rule Checking, IP Cores, Requirements Lifecycle Management, DO-254 Functional Verification, Embedded Solutions and Military/Aerospace solutions. www.aldec.com

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.